### **Datasheet**

DS000571

# CSG14K\_CSG8K

13.8Mp\_8.3Mp High Speed Global Shutter CMOS Image Sensor

v1-00 • 2020-Dec-15

## **Content Guide**

| 1                 | General Description                                      | 3  |

|-------------------|----------------------------------------------------------|----|

| 1.1<br>1.2<br>1.3 | Key Benefits & Features<br>Applications<br>Block Diagram | 3  |

| 2                 | Ordering Information                                     | 5  |

| 3                 | Pin Assignment                                           | 6  |

| 3.1<br>3.2        | Pin Diagram<br>Pin Description                           |    |

| 4                 | Absolute Maximum Ratings                                 | 9  |

| 5                 | Electrical Characteristics                               | 10 |

| 6                 | Typical Operating Characteristics                        | 12 |

| 6.1<br>6.2        | Electro-Optical Characteristics                          |    |

| 7                 | Functional Description                                   | 16 |

|          | Sensor Architecture                       | 10 |

|----------|-------------------------------------------|----|

| 7.2      | Operating the Sensor                      | 20 |

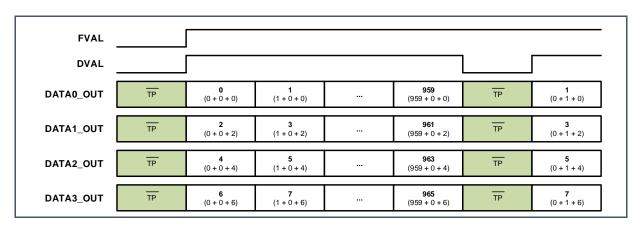

| 7.3      | Sensor Readout Format                     | 48 |

| 7.4      | Configuring the Sensor                    | 53 |

| 7.5      | Configuring Readout and Exposure          | 71 |

| 7.6      | Configuring the Output Data Format        | 84 |

| 7.7      | Configuring the On-Chip Data Processing . | 87 |

| 7.8      | Additional Features                       | 91 |

| 8        | Register Overview10                       | )4 |

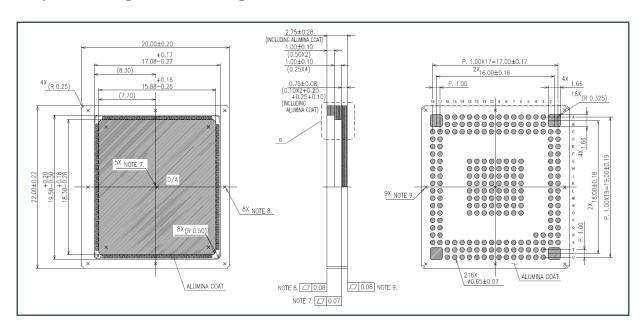

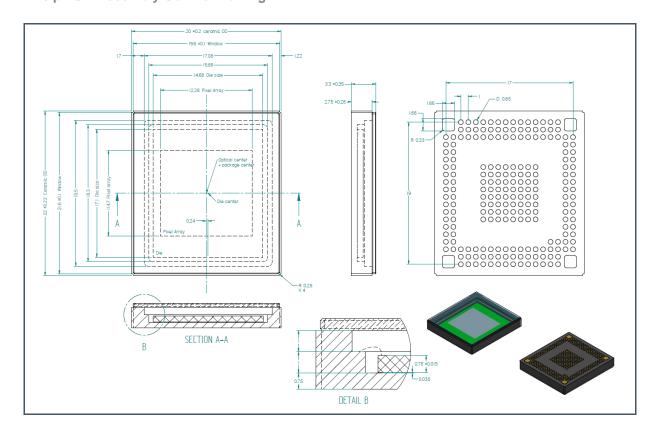

| 9        | Package Drawings & Markings.10            | 80 |

|          |                                           |    |

| 10       | Soldering & Storage                       |    |

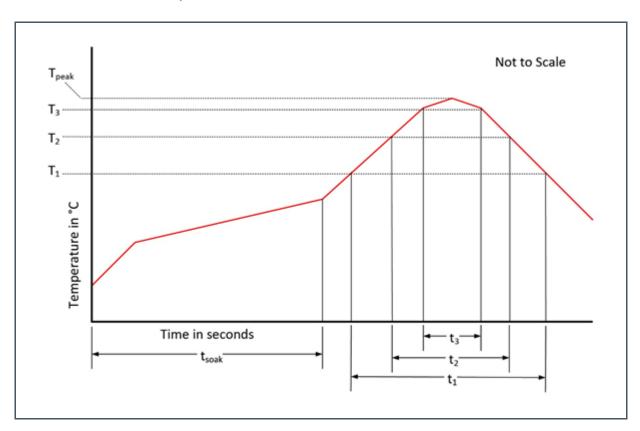

| 10       | Soldering & Storage Information11         | 10 |

| 10<br>11 |                                           |    |

## 1 General Description

The CSG14K\_CSG8K is a high speed CMOS image sensor family developed for machine vision and video applications. The image array consists of 3.2 µm pipelined global shutter pixels, which allow exposure during read out, while performing true CDS (Correlated Double Sampling) operation. The image sensor has 16 sub-LVDS data output channels. Each output channel runs at up to 1.25 Gbit/s, resulting in a frame rate of 140 fps (CSG14K) or 231 fps (CSG8K) in full resolution. Higher frame rates can be achieved in row-windowing mode or row-subsampling mode. These modes are all programmable using the SPI interface. All internal exposure and read out timings are generated by a programmable on-chip sequencer. External triggering and exposure programming is also possible. Extended optical dynamic range can be achieved by a dual exposure HDR (High Dynamic Range) mode. The image sensor also integrates black level clamping.

### 1.1 Key Benefits & Features

The benefits and features of CSG14K\_CSG8K, 13.8Mp\_8.3Mp High Speed Global Shutter CMOS Image Sensor, are listed below:

Figure 1: Added Value of Using CSG14K\_CSG8K

| Benefits                                      | Features                                                             |

|-----------------------------------------------|----------------------------------------------------------------------|

| High performance applications                 | 13.8 Mp resolution at 140/93.6 fps (CSG14K, 10/12-bit)               |

| High performance applications                 | 8.3 Mp resolution at 231/154 fps (CSG8K, 10/12-bit)                  |

| Capture fast moving objects                   | Global shutter pixel with true Correlated Double Sampling (true-CDS) |

| Use in low light conditions                   | Low noise and high sensitivity with on-chip noise reduction.         |

| Small camera size                             | 1" optical format in a 20 mm × 22 mm LGA package (CSG14K)            |

| Small camera size                             | 3/4" optical format in a 20 mm × 22 mm LGA package (CSG8K)           |

| Operation modes tailored to application needs | Programmable sensor timing & readout configuration                   |

### 1.2 Applications

- Machine Vision

- High-End Inspection

- Video / Broadcast

- Security

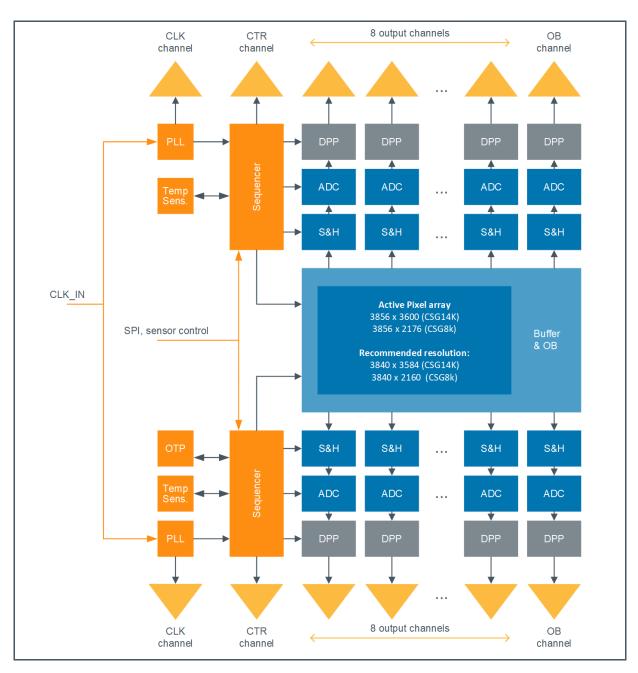

## 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2 : Functional Blocks of CSG14K\_CSG8K

## 2 Ordering Information

| Marking       | Mono/Color | Glass Type | Package | Delivery Form | Delivery Qty |

|---------------|------------|------------|---------|---------------|--------------|

| CSG14K-1E5MLA | Mono       | AR coated  | LGA     | Tray          | 40 pcs/tray  |

| CSG8K-1E5MLA  | Mono       | AR coated  | LGA     | Tray          | 40 pcs/tray  |

## 3 Pin Assignment

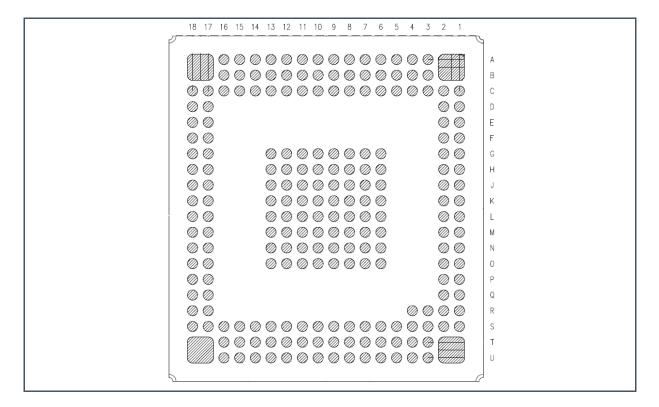

### 3.1 Pin Diagram

Figure 3: Pin Diagram

The center 8×8 pads have no functional use (internally not connected (NC)) and should be used for improved thermal conductance from the sensor to the camera.

The four large corner pads are internally NC and needed for solderability.

### 3.2 Pin Description

Figure 4: Pin Description of CSG14K\_CSG8K

| Pin Number     | Pin Name | Pin Type <sup>(1)</sup> | Description   |

|----------------|----------|-------------------------|---------------|

| C7, M2, S2, S7 | VDD33    | S                       | Analog supply |

| Pin Number                                                                           | Pin Name           | Pin Type <sup>(1)</sup> | Description                                             |

|--------------------------------------------------------------------------------------|--------------------|-------------------------|---------------------------------------------------------|

| K1, K17, K18, K2, L1, L17,<br>L18, L2, N17, O17                                      | VSS33              | G                       | Analog ground                                           |

| C1, C2, S1                                                                           | VDD33D             | S                       | IO supply                                               |

| J1, J2, M1                                                                           | VDDPIX             | S                       | Pixel supply                                            |

| A7, B14, B4, C11, C12, S11, S12, T14, T4, U7                                         | VDD12              | S                       | Digital supply                                          |

| A12, B3, B9, C16, C6, S16,<br>S6, T3, T9, U12                                        | VSS12              | G                       | Digital ground                                          |

| C14, C8, C9, S10, S14, S8, S9                                                        | VDD12C             | S                       | ADC supply                                              |

| C13, F1, F2, N1, N2, S13, S5                                                         | VSS12C             | G                       | ADC ground                                              |

| C10, P1                                                                              | VDD12_PLL          | S                       | PLL supply                                              |

| C5, P2                                                                               | VSS12_PLL          | G                       | PLL ground                                              |

| S15                                                                                  | -                  | G                       | Connect to VSS33                                        |

| C15                                                                                  | VDD45              | S                       | Regulator supply                                        |

| S17                                                                                  | VSSNEG             | S                       | Negative regulator supply                               |

| J18                                                                                  | VPIX1_H_IN         | S                       | Analog supply                                           |

| E18                                                                                  | VPIX1_L_IN         | S                       | Analog supply                                           |

| H18                                                                                  | VPIX2_H_IN         | S                       | Analog supply                                           |

| D18                                                                                  | VPIX2_L_IN         | S                       | Analog supply                                           |

| F18                                                                                  | VPIX3_H_IN         | S                       | Analog supply                                           |

| M17                                                                                  | VPIX3_L_IN         | S                       | Analog supply                                           |

| G18                                                                                  | VPIX4_H_IN         | S                       | Analog supply                                           |

| C18                                                                                  | VPIX4_L_IN         | S                       | Analog supply                                           |

| E1                                                                                   | SPI_CSN            | DI                      | SPI chip select                                         |

| E2                                                                                   | SPI_MISO           | DO                      | SPI master in/slave out data                            |

| D2                                                                                   | SPI_MOSI           | DI                      | SPI master out/slave in data                            |

| D1                                                                                   | SPI_CLK            | DI                      | SPI clock                                               |

| G2                                                                                   | REQ_FRAME          | DI                      | Request frame (stop exposure)                           |

| G1                                                                                   | REQ_EXP            | DI                      | Request exposure (start exposure)                       |

| H1                                                                                   | RST_N              | DI                      | Asynchronous hard reset                                 |

| H2                                                                                   | CLK_IN             | DI                      | Sensor input clock                                      |

| 01                                                                                   | JTAG_MODE          | DI                      | JTAG Mode select. Connect to VSS33 if JTAG is not used. |

| O2                                                                                   | SCAN_MODE          | DI                      | Reserved for test. Connect to VSS33.                    |

| Q2, Q1, R1, R2                                                                       | TDIG14             | DO                      | Digital test monitor                                    |

| U4, U3<br>U6, U5<br>T8, T7<br>U9, U8<br>U11, U10<br>T11, T10<br>U14, U13<br>T13, T12 | DOUT <i>_B_N/P</i> | HSO                     | Output data channel (i=18) at bottom                    |

| Pin Number              | Pin Name           | Pin Type <sup>(1)</sup> | Description                                |

|-------------------------|--------------------|-------------------------|--------------------------------------------|

| A4, A3                  |                    |                         |                                            |

| A6, A5                  |                    |                         |                                            |

| B8, B7                  |                    |                         |                                            |

| A9, A8<br>A11, A10      | DOUT <i>_T_N/P</i> | HSO                     | Output data channel (i=18) at top          |

| B11, B10                |                    |                         |                                            |

| A14, A13                |                    |                         |                                            |

| B13, B12                |                    |                         |                                            |

| U16, U15                | DOUT_OB_B_N/P      | HSO                     | Optical black data channel at bottom       |

| A16, A15                | DOUT_OB_T_N/P      | HSO                     | Optical black data channel at top          |

| T6, T5                  | DOUT_CTR_B_N/P     | HSO                     | Control channel at bottom                  |

| B6, B5                  | DOUT_CTR_T_N/P     | HSO                     | Control channel at top                     |

| T16, T15                | DOUT_CLK_B_N/P     | HSO                     | Clock channel at bottom                    |

| B16, B15                | DOUT_CLK_T_N/P     | HSO                     | Clock channel at top                       |

| S4, S3                  | -                  | G                       | connect to VSS33                           |

| C4, C3                  | -                  | G                       | connect to VSS33                           |

| P17, Q17, R17           | -                  | G                       | connect to VSS33                           |

| O18, P18, Q18, M18, N18 | REFA04             | Α                       | Analog reference                           |

| R18                     | VBGAP              | Α                       | Analog reference                           |

| S18                     | BIAS_IDAC_RES      | Α                       | Analog reference, connect to bias resistor |

| E17                     | VPIX1_L_OUT        | Α                       | Analog reference                           |

| J17                     | VPIX1_H_OUT        | Α                       | Analog reference                           |

| D17                     | VPIX2_L_OUT        | Α                       | Analog reference                           |

| H17                     | VPIX2_H_OUT        | А                       | Analog reference                           |

| C17                     | VPIX4_L_OUT        | А                       | Analog reference                           |

| G17                     | VPIX4_H_OUT        | А                       | Analog reference                           |

| F17                     | VPIX3_H_OUT        | А                       | Analog reference                           |

| R3, R4                  | -                  | NC                      | Do not connect                             |

#### (1) Explanation of abbreviations:

DI Digital Input

DO Digital Output

HSO High Speed Output

A Analog reference

G Ground

S Supply

NC Not Connected

## 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5

Absolute Maximum Ratings of CSG14K\_CSG8K

| Symbol             | Parameter                              | Min   | Max   | Unit | Comments                                     |

|--------------------|----------------------------------------|-------|-------|------|----------------------------------------------|

| Electrical Para    | meters                                 |       |       |      |                                              |

| VDD12              | Logic Supply Voltage of digital core   | - 0.3 | 1.7   | V    |                                              |

| VDD12_PLL          | Logic Supply Voltage of PLL analog     | - 0.3 | 1.7   | V    |                                              |

| VDD12C             | Logic Supply Voltage of ADC            | - 0.3 | 1.7   | V    |                                              |

| VDD33D             | I/O Supply Voltage for CMOS I/O's      | - 0.3 | 3.6   | V    |                                              |

| VDD33              | Main Analog Supply Voltage             | - 0.3 | 3.6   | V    |                                              |

| VDDPIX             | Pixel Array Supply Voltage             | - 0.3 | 3.6   | V    |                                              |

| VDD45              | Positive Regulators                    | - 0.3 | 4.7   | V    |                                              |

| VSSNEG             | Negative Regulators                    | - 1.5 | 0.3   | V    |                                              |

| I <sub>SCR</sub>   | Input Current (latch-up immunity)      |       | ± 100 | mA   | JEDEC JESD78D Nov 2011                       |

| Electrostatic D    | Discharge                              |       |       |      |                                              |

| ESD <sub>HBM</sub> | Electrostatic Discharge HBM            |       | ± 2   | kV   | JS-001-2014                                  |

| ESD <sub>CDM</sub> | Electrostatic Discharge CDM            |       | ± 250 | V    | JEDEC JESD22-C101F Oct<br>2013               |

| Temperature F      | Ranges and Storage Conditions          |       |       |      |                                              |

| TJ                 | Operating Junction<br>Temperature      | -30   | 85    | °C   |                                              |

| T <sub>STRG</sub>  | Storage Temperature Range              | -30   | 40    | °C   |                                              |

| RH <sub>NC</sub>   | Relative Humidity (non-<br>condensing) | 30    | 60    | %    | Storage condition                            |

| MSL                | Moisture Sensitivity Level             |       | 3     |      | Represents a maximum floor life time of 168h |

| Bump Temper        | ature (soldering)                      |       |       |      |                                              |

| T <sub>PEAK</sub>  | Peak Temperature                       | 245   |       | °C   | Solder Profile in chapter 10                 |

## **5** Electrical Characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Electrical Characteristics of CSG14K\_CSG8K

| Symbol          | Parameter                              | Conditions             | Min           | Тур        | Max       | Unit |

|-----------------|----------------------------------------|------------------------|---------------|------------|-----------|------|

| Power Supplies  |                                        |                        |               |            |           |      |

| VDD12           | Logic supply voltage of digital core   |                        | 1.25          | 1.28       | 1.32      | V    |

| VDD12_PLL       | Logic supply voltage of PLL analog     |                        | 1.25          | 1.28       | 1.32      | V    |

| VDD12C          | Logic supply voltage of ADC            |                        | 1.25          | 1.28       | 1.32      | V    |

| VDD33D          | I/O supply voltage for CMOS I/O's      |                        | 3.25          | 3.30       | 3.35      | V    |

| VDD33           | Main analog supply voltage             |                        | 3.25          | 3.30       | 3.35      | V    |

| VDDPIX          | Pixel array supply voltage             |                        | 3.25          | 3.30       | 3.35      | V    |

| VDD45           | Positive regulators                    |                        | 4.4           | 4.5        | 4.6       | V    |

| VSSNEG          | Negative regulators                    |                        | -1.4          | -1.3       | -1.2      | V    |

| IDD12           | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 306<br>321 |           | mA   |

| IDD12_PLL       | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 13<br>13   |           | mA   |

| IDD12C          | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 105<br>151 |           | mA   |

| IDD33D          | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 116<br>116 |           | mA   |

| IDD33           | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 246<br>251 |           | mA   |

| IDDPIX          | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 106<br>106 |           | mA   |

| IDD45           | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 25<br>25   |           | mA   |

| ISSNEG          | Supply current <sup>(1)</sup>          | Idle<br>Running        |               | 125<br>126 |           | mA   |

| Ptot            | Total power consumption <sup>(1)</sup> | Idle<br>Running        |               | 2.0        |           | W    |

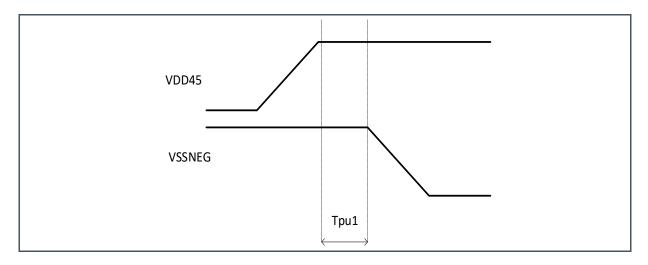

| Tpu1            | Settling time after VDD45 power-up     |                        | 100           | -          | -         | μs   |

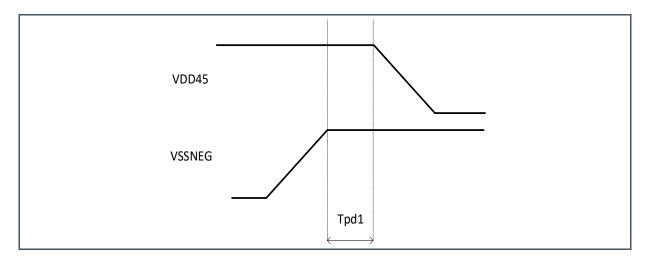

| Tpd1            | Settling time after VSSNEG power-down  |                        | 100           | -          | -         | μs   |

| Digital I/O     |                                        |                        |               |            |           |      |

| V <sub>IH</sub> | High level input voltage               |                        | 0.7*VDD<br>33 |            | VDD33     | V    |

| V <sub>IL</sub> | Low level input voltage                |                        | 0             |            | 0.3*VDD33 | V    |

| V <sub>OH</sub> | High level output voltage              | I <sub>OH</sub> =12 mA | VDD33-<br>0.6 |            |           | V    |

| Symbol               | Parameter                             | Conditions             | Min                         | Тур  | Max  | Unit   |

|----------------------|---------------------------------------|------------------------|-----------------------------|------|------|--------|

| V <sub>OL</sub>      | Low level output voltage              | I <sub>OL</sub> =12 mA |                             |      | 0.4  | V      |

| Cı                   | Input load                            |                        |                             |      | 3    | рF     |

| Co                   | Output load                           |                        |                             |      | 20   | pF     |

| f <sub>CLK_IN</sub>  | CLK_IN frequency                      |                        | 12                          |      | 20   | MHz    |

| DC <sub>CLK_IN</sub> | CLK_IN duty cycle                     |                        | 30                          | 50   | 70   | %      |

| f <sub>SPI_CLK</sub> | SPI input clock frequency             |                        |                             |      | 15   | MHz    |

| t <sub>setup</sub>   | SPI setup time                        |                        | 10                          |      |      | ns     |

| t <sub>hold</sub>    | SPI hold time                         |                        |                             |      | 0    | ns     |

| t <sub>REQ</sub>     | REQ_FRAME/EXP pulse width             |                        | 2 x<br>t <sub>CLK_PIX</sub> |      | -    | ns     |

| Sub-LVDS Inte        | erface                                |                        |                             |      |      |        |

| DR <sub>HS</sub>     | Output data rate                      |                        | 0.25                        | 1.25 | 1.25 | Gbit/s |

| V <sub>FCM</sub>     | Fixed common mode voltage             |                        | 0.8                         | 0.9  | 1    | V      |

| V <sub>OD</sub>      | Differential voltage swing            |                        | 100                         | 150  | 200  | mV     |

| Ro                   | Output impedance                      |                        | 40                          | 100  | 140  | Ohm    |

| D <sub>R0</sub>      | Impedance mismatch                    |                        |                             |      | 10   | %      |

| I <sub>OD</sub>      | Drive current                         |                        | 0.83                        |      | 2    | mA     |

| ΔIOD                 | IOD variation                         |                        |                             |      | 15   | %      |

| t <sub>R</sub>       | V <sub>OD</sub> rise time (20 %-80 %) |                        | 300                         |      | 400  | ps     |

| t <sub>F</sub>       | V <sub>OD</sub> fall time (80 %-20 %) |                        | 300                         |      | 400  | ps     |

<sup>(1)</sup> Current and Power numbers measured in IMG.4 mode (12b default)

## **6 Typical Operating Characteristics**

### 6.1 Electro-Optical Characteristics

Below are the typical electro-optical specifications of CSG14K\_CSG8K, when operated in the 12-bit default mode. These are typical values with typical supplies at room temperature.

Figure 7: Electro-Optical Characteristics

| Parameter                       | Value                                   | Remark                                                                                                               |

|---------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| A .:                            | 3856 (H) × 3600 (V)                     | CSG14K                                                                                                               |

| Active pixels                   | 3856 (H) × 2176 (V)                     | CSG8K                                                                                                                |

| Pixel pitch                     | $3.2 \times 3.2 \mu\text{m}^2$          |                                                                                                                      |

| Optical format                  | 1"                                      |                                                                                                                      |

| Pixel type                      | Global shutter<br>with true CDS         | Allows fixed pattern noise correction and reset (kTC) noise canceling by true correlated double sampling (true-CDS). |

| Shutter type                    | Pipelined global shutter                | Exposure of next image during readout of the previous image.                                                         |

| Full well charge <sub>sat</sub> | 10500 e <sup>-</sup>                    | Normal mode, 8 lux conditions                                                                                        |

| Conversion gain                 | 0.386 DN/e <sup>-</sup>                 | Normal mode, unity gain                                                                                              |

| Responsivity                    | 0.254 DN/photon<br>0.276 A/W            | @510 nm (with micro-lenses)                                                                                          |

| Temporal noise                  | 3.7 e <sup>-</sup>                      | Normal mode                                                                                                          |

| Dynamic range                   | 69.1 dB                                 | Normal mode                                                                                                          |

| SNR <sub>MAX</sub>              | 40.0 dB                                 | Normal mode                                                                                                          |

| Shutter efficiency<br>1/PLS     | 1/11130                                 | At 520 nm, f/8.                                                                                                      |

| Dark current (DC)               | 32.9 e <sup>-</sup> /s                  | @ 60 °C sensor junction temperature                                                                                  |

| DC doubling                     | 6.59 °C                                 | The DC doubles every 6.59 °C increase                                                                                |

| DCNU                            | 16.2 e-/s                               | Dark current non uniformity @60 °C sensor temperature                                                                |

| DSNU <sub>1288</sub>            | 1.9 e <sup>-</sup>                      | Dark signal non uniformity                                                                                           |

| PRNU <sub>1288</sub>            | 0.89 %                                  | Photo response non-uniformity RMS of signal                                                                          |

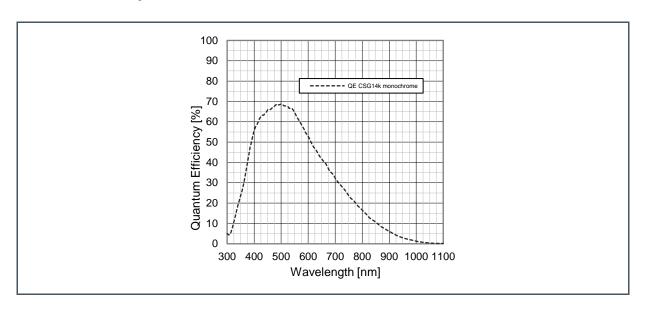

| Quantum efficiency              | 64 / 66 / 51 / 10 %                     | @ 450 / 510 / 600 / 850 nm (mono) Quantum Efficiency (with micro-lenses)                                             |

| Data interface standard         | Sub-LVDS                                | Similar to CMV sensor family                                                                                         |

| Sub-LVDS outputs                | 16 Data<br>1 Control<br>1 Clock<br>2 OB | Less outputs selectable at reduced frame rate                                                                        |

| Parameter                 | Value             | Remark                                                       |

|---------------------------|-------------------|--------------------------------------------------------------|

| Output interface bit rate | 1.25 Gbit/s       | Per data channel (maximum)                                   |

|                           | 140 fps           | CSG14K, 10-bit                                               |

| Frame rate (1)            | 93 fps            | CSG14K, 12-bit                                               |

| Frame rate V              | 231 fps           | CSG8K, 10-bit                                                |

|                           | 154 fps           | CSG8K, 12-bit                                                |

| Timing generation         | On-chip           | Possibility to control exposure time through external pin.   |

| Programmable registers    | Sensor parameters | Window coordinates, timing parameters, exposure time, offset |

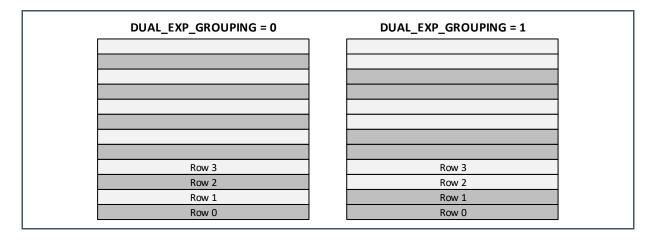

| HDR mode                  | Interleaved       | 2 exposure times for odd/even rows                           |

| ADC                       | 10-bit            | Column ADC                                                   |

| ADC                       | 12-bit            | Column ADC                                                   |

| Cover glass               | D263Teco          |                                                              |

| RoHS/REACH                |                   |                                                              |

| MSL                       | 3                 | Represents a maximum floor life time of 168 hours            |

| Mass                      | 3.223 g           |                                                              |

<sup>(1)</sup> Higher frame rate possible in row windowing mode or when operating in 10-bit mode. Based on recommended pixel area.

The following table details the expected typical performance in the various readout configuration modes.

Figure 8:

Typical Performance Values for the Various Readout Configurations

| Parameter                                                           | 10 b Default<br>(IMG.1) | 10 b Short<br>Exp. Mode<br>(IMG.2) | 10 b Small<br>Window<br>Mode<br>(IMG.3) | 12 b Default<br>(IMG.4) | 12 b Short<br>Exp. Mode<br>(IMG.5) | 12 b Binning<br>Mode<br>(IMG.7) |

|---------------------------------------------------------------------|-------------------------|------------------------------------|-----------------------------------------|-------------------------|------------------------------------|---------------------------------|

| ADC resolution                                                      | 10 b                    |                                    |                                         | 12 b                    |                                    |                                 |

| Output image<br>resolution<br>(recommended<br>pixels) for<br>CSG14K | 3840 (h)<br>3584 (v)    |                                    | 3840 (h)<br>400 (v)                     | 3840 (h)<br>3584 (v)    |                                    | 1920 (h)<br>1792 (v)            |

| Output image<br>resolution<br>(recommended<br>pixels) for CSG8K     | 3840 (h)<br>2160 (v)    |                                    | 3840 (h)<br>400 (v)                     | 3840 (h)<br>2160 (v)    |                                    | 1920 (h)<br>1080 (v)            |

| Full well charge                                                    | 10000 e-                |                                    | 9800 e-                                 | 10500 e-                |                                    | 40600 e-                        |

| Conversion gain                                                     | 0.10 DN/e-              |                                    |                                         | 0.38 DN/e-              |                                    | 0.10 DN/e-                      |

| Temp. noise                                                         | 5.6 e-                  |                                    |                                         | 3.7 e-                  |                                    | 12.4 e-                         |

| Dynamic range                                                       | 65.1 dB                 | 65.1 dB                            | 64.9 dB                                 | 4.9 dB 69.1 dB 69.1 dB  |                                    | 70.3 dB                         |

| SNRmax                                                              | 39.8 dB                 | 39.8 dB                            | 39.7 dB                                 | 40.0 dB                 | 40.0 dB                            | 45.9 dB                         |

| DSNU (1288)                                                         | 1.9 e-                  | 1.8 e-                             | 20.7 e-                                 | 1.9 e-                  | 1.7 e-                             | 3.4 e-                          |

| Maximum FR at recommended resolution (CSG14K)                       | 140 fps                 | 140 fps                            | NA                                      | 93 fps                  | 93 fps 93 fps                      |                                 |

| Maximum FR at recommended resolution (CSG8K)                        | 231 fps                 | 228 fps                            | NA                                      | 153 fps                 | 153 fps 153 fps                    |                                 |

| Maximum FR (100 lines ROI, 100 μs exposure time)                    | 3829 fps                | 3017 fps                           | 4793 fps                                | 2625 fps                | 2255 fps                           | 3361 fps                        |

| Minimum<br>exposure time<br>(t <sub>exp,min</sub> )                 | 36.7 µs                 | 7.9 µs                             | 11.2 µs                                 | 11.2 µs 46.2 µs 10.0 µs |                                    | 36.9 µs                         |

| Maximum<br>exposure time<br>(t <sub>exp,max</sub> )                 | NA                      | 100 µs                             | NA                                      | NA                      | NA 100 μs                          |                                 |

| I/F DR (at maximum FR)                                              | 1250 Mbit/s             | 1250 Mbit/s                        | 1250 Mbit/s                             | 1000 Mbit/s             | 1000 Mbit/s                        | 1000 Mbit/s                     |

| Power consumption                                                   | 2.02 W                  | 2.23 W                             | 2.19 W                                  | 1.93 W                  | 2.13 W                             | 1.86 W                          |

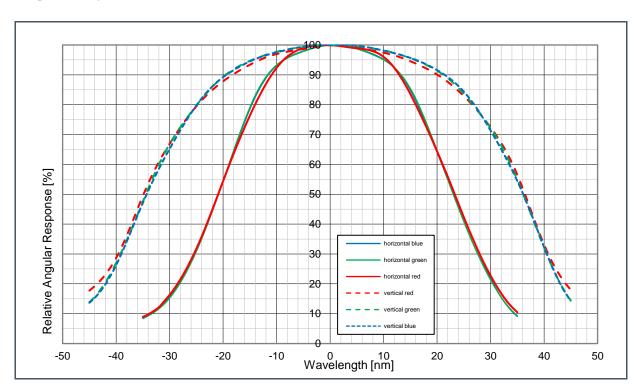

## 6.2 Spectral Characteristics

Figure 9: Quantum Efficiency Mono

Figure 10: Angular Response Color

## 7 Functional Description

#### 7.1 Sensor Architecture

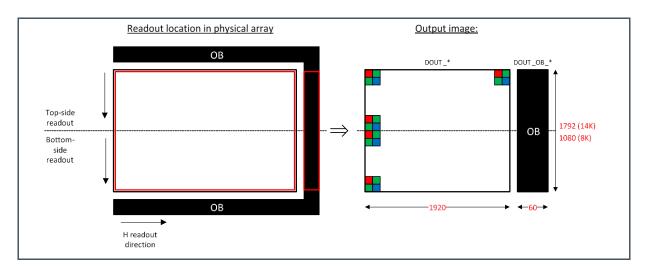

Figure 2 shows a high-level representation of the chip architecture for the CSG14K\_CSG8K sensor. The drawing shows the pixel array and the periphery around it that enables the control and readout of the pixels.

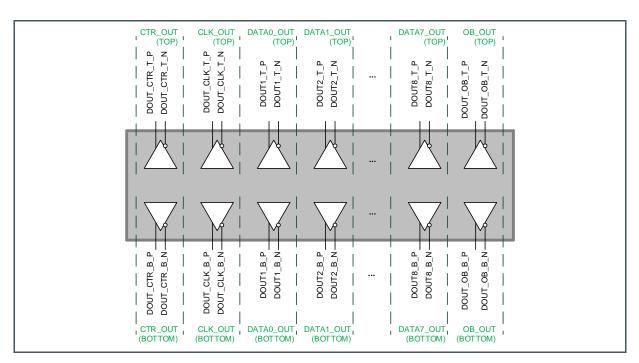

The core of the image sensor is made up from the pixel array, which is driven from two sides through row logic and drivers. The pixel data is read out, row by row, using a data path consisting of an sample and hold stage (S&H), analog-to-digital converter (ADC) and a digital data post-processing (DPP) block. The top part of the pixel array is read out via the top outputs, while the bottom part is read via the bottom outputs.

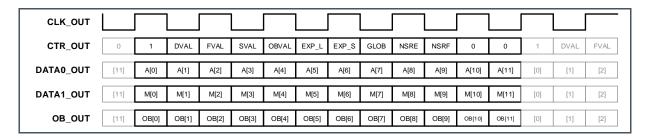

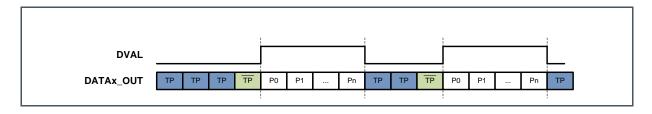

The converted data is sent, pixel by pixel, to a configurable number of data output channels. An additional control (CTR) channel provides synchronization information about the data on the data channels, while a specific CLK channel can be used to sample the data channels.

An optional output channel allows reading out OB pixel columns on the right side of the pixel array.

The on-chip PLL transforms a low-frequency CMOS input clock into all the high frequency clocks needed to operate the sensor.

An on-chip sequencer controls the sensor operation and contains SPI programmable registers.

Two on-chip temperature sensors and an OTP memory are available.

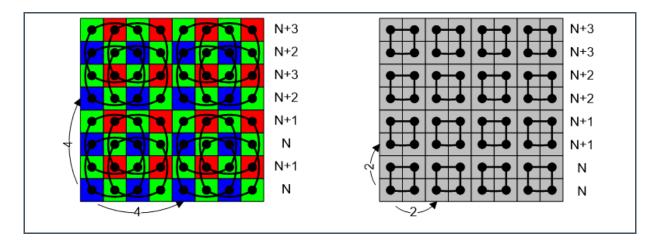

#### 7.1.1 Pixel Array

This section is split-up between CSG14K and CSG8K. The pixel array of the CSG8K is very similar to the pixel array of the CSG14K, except that some rows cannot be read out to limit vertical resolution in CSG8K. Refer to chapter 7.5.3 for more details on which rows can be addressed.

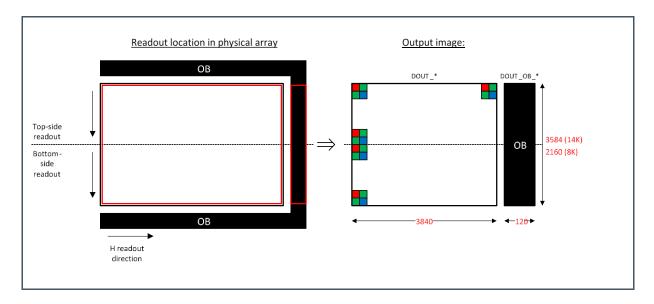

#### Pixel Array of the CSG14K

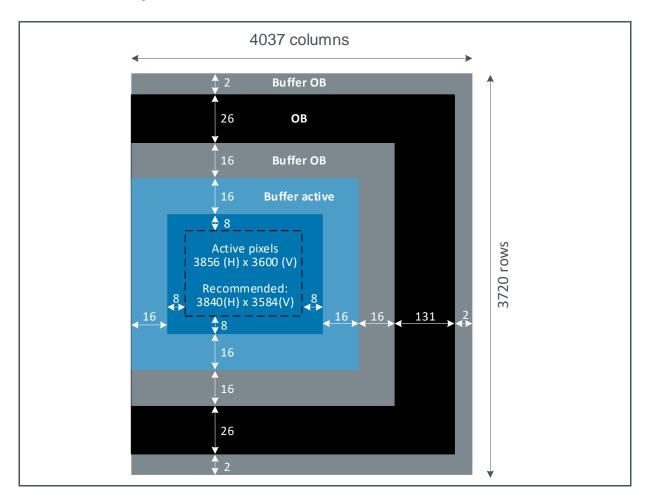

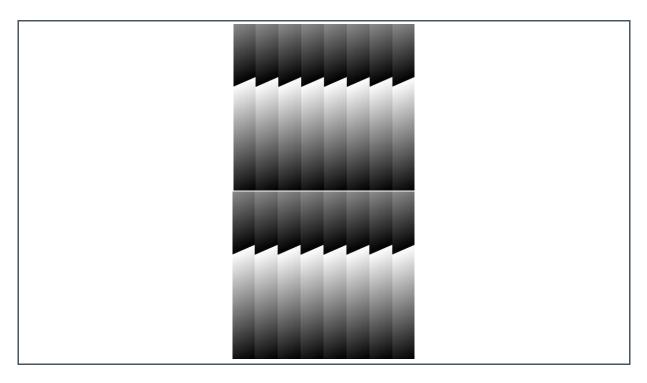

Figure 11 shows the complete pixel array.

Figure 11: CSG14K Pixel Array

The physical resolution of the complete pixel array is 4037 (H) × 3720 (V) pixels.

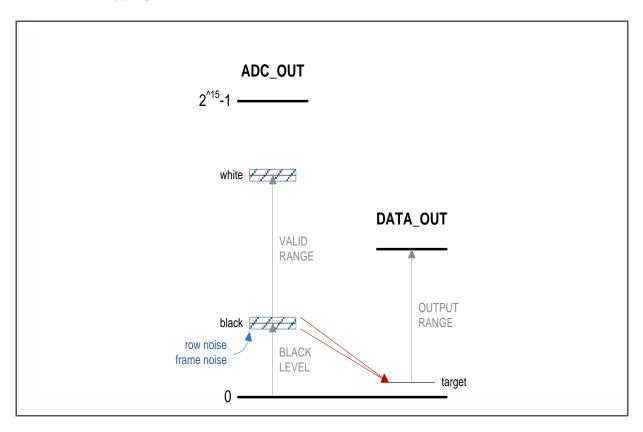

The pixel array can be split up in three parts: active pixels, optical black pixels (OB), and buffer pixels (around both the active array and OB perimeter). The OB pixels are used for internal row clamping, which improves row noise and allows setting a pre-defined black level. The buffer pixels form a guard ring around the active pixels. The buffer pixels are optically active, but are not guaranteed to meet the optical specifications. The OB and buffer pixel columns can be read out via the OB output channel.

The resolution of the active pixel array is 3856 (H)  $\times$  3600 (V) pixels. This is further split into a ring of 8 pixels on every side for color reconstruction and an optically centered recommended pixel array with a resolution of 3840 (H)  $\times$  3584 (V) pixels. The recommended array is 12.29 mm  $\times$  11.47 mm, which is a 1" optical format.

Micro-lenses are placed on the pixels for improved quantum efficiency and fill factor.

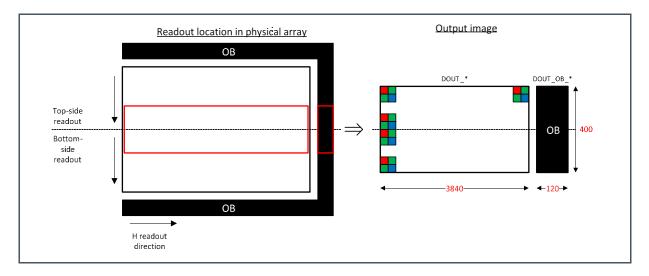

#### Pixel Array of the CSG8K

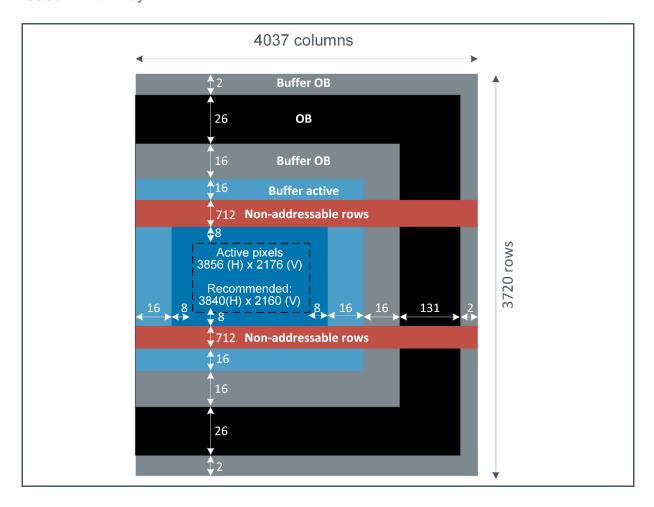

Figure 12 shows the complete pixel array.

Figure 12: CSG8K Pixel Array

The physical resolution of the complete pixel array is 4037 (H) × 3720 (V) pixels.

The resolution of the active pixel array is 3856 (H)  $\times$  2176 (V) pixels. This is further split into a ring of 8 pixels on every side for color reconstruction and an optically centered recommended pixel array with a resolution of 3840 (H)  $\times$  2160 (V) pixels. The recommended array is 12.29 mm  $\times$  6.91 mm, which is a 3/4" optical format.

Micro-lenses are placed on the pixels for improved quantum efficiency and fill factor.

#### 7.1.2 Analog Front End

The analog front end consists of circuitry to prepare the signal for ADC conversion also called the sample & hold stage (S&H).

#### 7.1.3 ADC

The column ADC converts the analog pixel value to a 10/12-bit value.

#### 7.1.4 DPP

The DPP blocks perform digital operations on the visible pixel data: digital offset, digital gain, row noise correction.

#### 7.1.5 Sub-LVDS Outputs

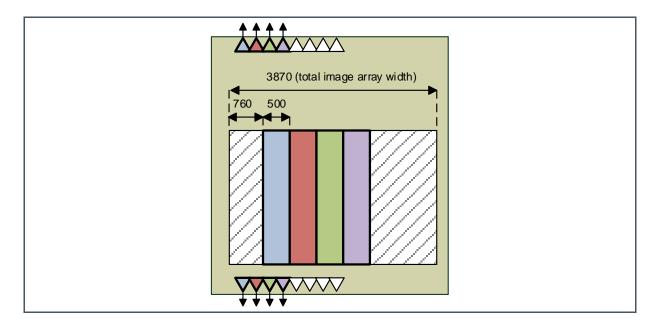

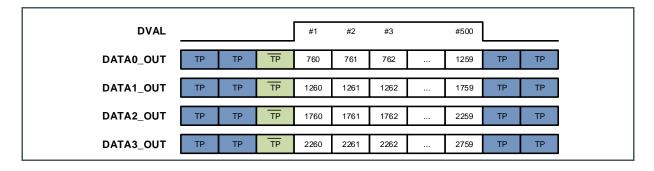

The sensor has 16 data channels to output the processed data. Every channel outputs the data of 480 columns when reading the recommended pixel array. Multiplexing the data on fewer outputs is supported as well.

#### 7.1.6 Sequencer

The on-chip sequencer will generate all required control signals to operate the sensor from only a few external control signals. This sequencer can be activated and programmed through the SPI interface.

The sequencer includes the following features:

- SPI protocol and register banks management.

- Exposure and frame timing generation based on external inputs or internal settings.

- Dual exposure HDR mode.

- Y-windowing, Y-subsampling and binning.

- Statistics data gathering.

#### 7.1.7 SPI Interface

The SPI interface is used to load the on-chip registers with settings to configure the image sensor. Features like exposure time, windowing, and subsampling are programmed using this interface. The settings in the on-chip registers can also be read back for test and debug of the surrounding system.

#### 7.1.8 Temperature Sensor

Two on-chip thermal sensors are included (one on the top right side and one on the bottom right side of the pixel array). The temperature data is read out through the SPI interface.

#### 7.1.9 PLL

Various clock frequencies are required internally to operate the sensor. These are derived from a single input frequency using an on-chip PLL. Through configuration over SPI, a range of input clock frequencies is supported.

The main internal clocks are:

- CLK\_ADC is the PLL output clock and is used to operate the ADC.

- CLK\_SER is the sub-LVDS output clock (625 MHz for 1.25 Gbit/s).

- CLK\_PIX is the pixel clock and has a ratio of:

- 1:5 of CLK\_SER in 10-bit ADC mode

- 1:6 of CLK\_SER in 12-bit ADC mode

#### **7.1.10 OTP Memory**

A non-volatile, one time programmable memory is included on-chip. This is programmed with unique identifier and temperature sensor calibration data.

### 7.2 Operating the Sensor

This section explains how to connect and power the sensor, as well as basic recipes of how to configure the sensor in a certain operation mode.

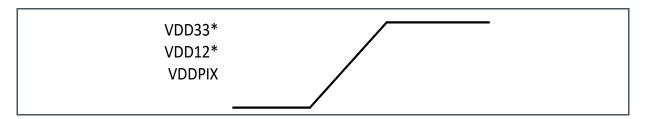

#### 7.2.1 Power Supplies

#### **External Power Supplies**

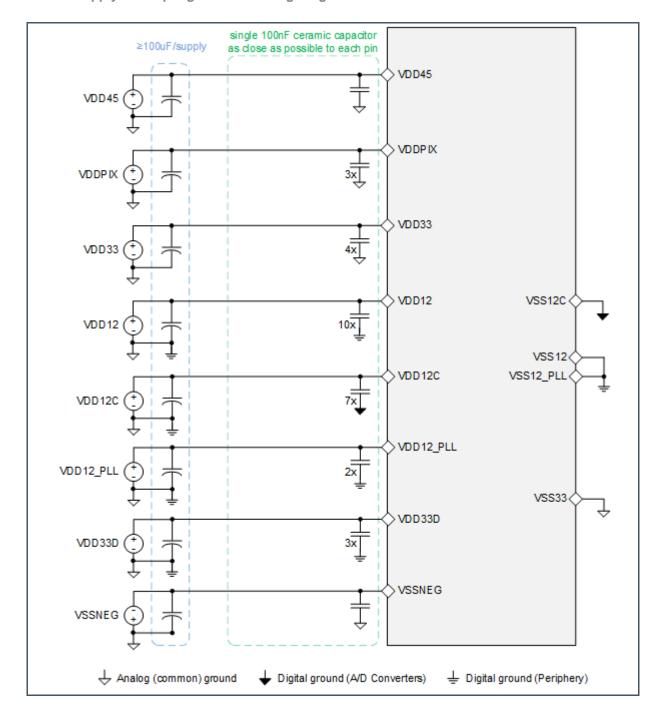

To power the sensor, eight externally generated supplies are required as listed in Figure 6. A Figure 6 distinction is made between digital supplies (VDD12, VDD12C, VDD33D, VDD12\_PLL) and analog supplies (VDD33, VDDPIX, VDD45, VSSNEG). Avoid using switching power supplies when possible, especially for the analog supplies.

Sufficient bulk (at the regulators) and local (at the sensor pins) decoupling is needed, see Figure 13. In case of multiple pins for the same supply, local decoupling must be foreseen for each pin (e.g. 3 capacitors for the 3 VDDPIX pins). Separate ground planes must be provided to minimize coupling.

For optimal noise performance, it is advised to keep the analog and digital ground nets separated and connect them together as close as possible to the external supply regulators.

Figure 13 :

Power Supply Decoupling and Grounding Diagram

#### Biasing (on-chip regulators)

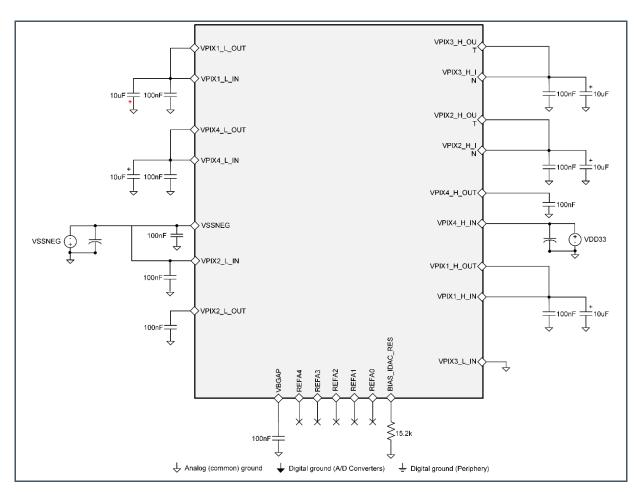

Operating the pixel array requires multiple different biasing supply levels. These supply levels can be generated using on-chip regulators. The chip contains 2 types of regulators, for positive supply levels and negative supply levels. The regulator output voltages are controlled using the SPI interface.

Internally, the supply regulators are not connected to the actual image sensor. Connections have to be made on PCB level (from a  $Vxx\_H/L\_OUT$  pin to a  $Vxx\_H/L\_IN$  pin). In addition, each supply regulator requires to be decoupled by a 10  $\mu$ F and 100 nF capacitor. **ams** recommends to use at least X7R-rated ceramic capacitors.

To obtain an accurate bias reference in the sensor, an external bias resistor of 15.2 k $\Omega$  must be placed between BIAS\_IDAC\_RES and ground. It is advised to use a low tolerance ( $\pm$  1%) and low temperature coefficient (50 ppm/°C or better).

Next figure shows the positive and negative voltage regulator as well as the bias connections.

Figure 14:

On-Chip Regulators Connection Diagram

After power-up of the sensor, the recommended register settings will set the correct supply levels for these regulators. Figure 14 gives an overview of the available supply regulators, the connection to the bias pin and the required voltage on that pin.

Figure 15: Bias Voltages

| Regulator Pin | Туре          | Bias Pin      | Voltage [V] |

|---------------|---------------|---------------|-------------|

| -             | Analog ref    | VBGAP         | 1.24        |

| -             | Analog ref    | BIAS_IDAC_RES | 1.24        |

| VPIX1_L_OUT   | Pixel control | VPIX1_L_IN    | -0.70       |

| VDD33 (ext)   | Pixel control | VPIX4_H_IN    | 3.30        |

| VPIX1_H_OUT   | Pixel control | VPIX1_H_IN    | 4.13        |

| VPIX3_H_OUT   | Pixel control | VPIX3_H_IN    | 3.83        |

| VPIX2_H_OUT   | Pixel control | VPIX2_H_IN    | 3.53        |

| VPIX4_L_OUT   | Pixel control | VPIX4_L_IN    | 0.73        |

| VSSNEG        | Pixel control | VPIX2_L_IN    | -1.30       |

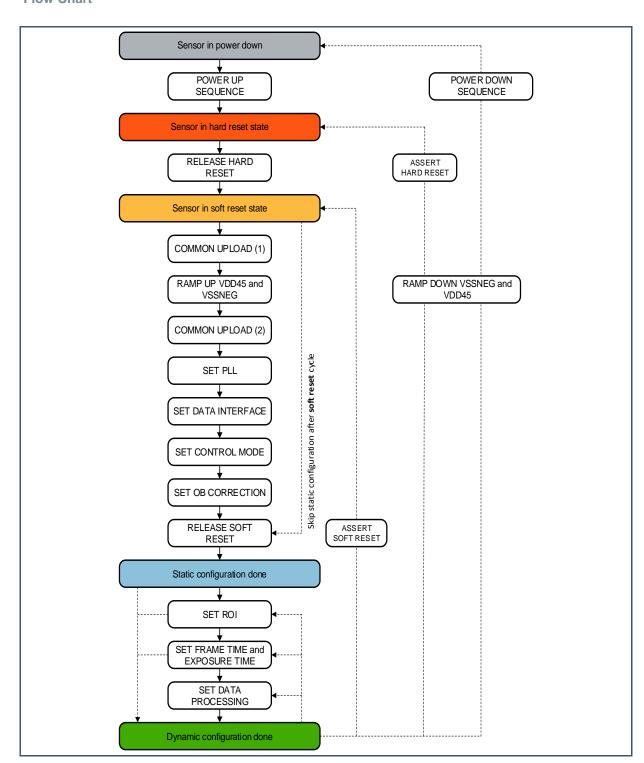

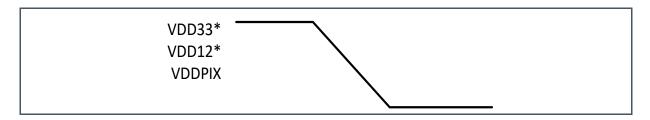

#### 7.2.2 Startup Sequence

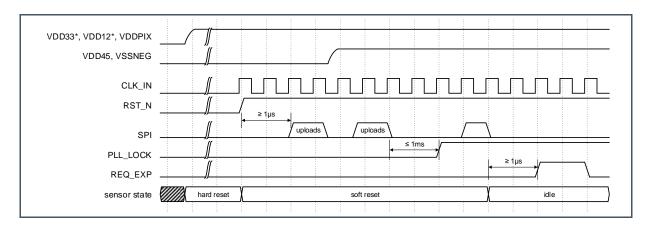

After the supply power-up sequence, the general sequence below (also shown in Figure 16) must be followed to configure and start operating the sensor. Deviating from the order or timing can lead to the sensor being in an unknown or unstable state.

The sensor hard reset pin, RST\_N, must be asserted ('0') during the supply ramp-up to initialize the sensor in the hard reset state. By releasing RST\_N ('1'), the sensor moves to soft reset state. CLK\_IN can be started during either the hard reset or during soft reset state (there is no relation to the releasing of RST\_N). During the soft reset state, the recommended SPI uploads must be executed (see section 7.4.3). This includes ramping up VDD45 and VSSNEG, and enabling the PLL, which locks after maximally 1 ms. After the PLL has locked, the sensor can be moved from soft reset state to idle state through a short SPI upload.

In idle state, the sensor waits for an exposure request to begin grabbing, for example with the REQ\_EXP pin (depending on the configured sensor control mode).

As indicated in the figure, a non-overlap of 1 µs must be respected between each sensor state change and the next action.

Figure 16: Power-Up Sequence (not to scale)

#### 7.2.3 Clocking

The sensor has two CMOS clock inputs: SPI\_CLK and CLK\_IN. SPI\_CLK is part of the SPI interface used to configure the sensor. All other internal sensor clocks are derived from the PLL running on CLK\_IN.

Refer to section 5 for the electrical specifications of the input clocks and to section 7.4.3 for the configuration procedure of the PLL.

#### 7.2.4 SPI and Register Access

The sensor operation must be configured by uploading register settings. These static register values control the behavior of the sequencer on the chip, but also of all the analog and mixed-signal blocks. To write and read register settings the SPI interface is used.

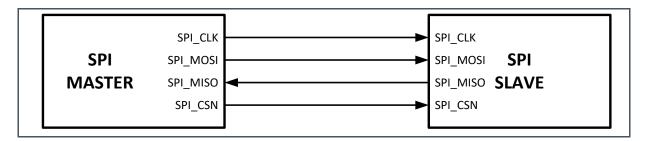

The SPI (Serial Peripheral Interface) consists of four wires, as shown in Figure 17.

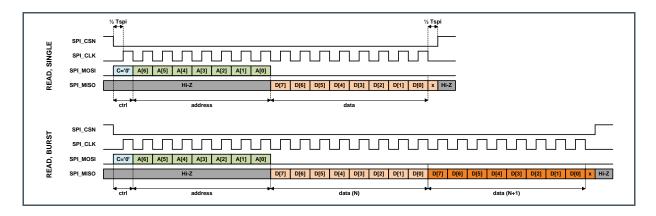

The CSG14K\_CSG8K image sensor always operates as the SPI slave. A single SPI access always consists of:

- Transfer of a control bit from master to slave to specify the transfer direction (read or write).

- Transfer of 7-bit register address from master to slave.

- Transfer of 8-bit data from master to slave (write operation) or from slave to master (read operation).

Figure 17: SPI Signal Overview

| Pin Name | Direction    | Purpose                |

|----------|--------------|------------------------|

| SPI_CSN  | Sensor Input | Active-low chip select |

| Pin Name | Direction     | Purpose                                      |

|----------|---------------|----------------------------------------------|

| SPI_CLK  | Sensor Input  | Rising-edge triggered clock for SPI protocol |

| SPI_MOSI | Sensor Input  | Data moving from master to slave             |

| SPI_MISO | Sensor Output | Data moving from slave to master             |

Data is written to the registers of the SPI slave over the SPI\_MOSI wire. The data written to the programming registers can also be read out over this same SPI interface, using the SPI\_MISO wire. SPI\_CSN is an active-low chip select that enables the SPI slave. The details of the timing and data format are described below.

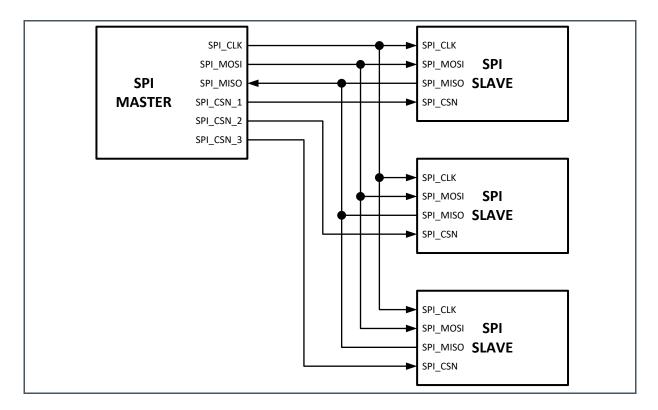

Figure 18: SPI Connection Diagram

When using multiple image sensors, the SPI\_CLK and SPI\_MOSI can be shared among them. The SPI\_CSN operates as a chip select for each of the slaves. The SPI\_MISO can also be shared on a bus because it is tri-stated when it is not used. This configuration of one master and multiple slaves is shown in Figure 18.

Figure 19: SPI with 1 Master and 3 Slaves

An SPI access always consists of the transfer of the following bits (in this order), as given in Figure 19

Figure 20: SPI Bits Transfer Sequence

| Phase | # Bits | Via      | Purpose                                                               |

|-------|--------|----------|-----------------------------------------------------------------------|

| CTRL  | 1      | SPI_MOSI | Control bit indicating SPI access direction (1 for write, 0 for read) |

| ADDR  | 7      | SPI_MOSI | Address (0-127) of register to be accessed                            |

|       |        | SPI_MOSI | Data written to N consecutive register addresses, starting at ADDR    |

| DATA  | N*8    | SPI_MISO | Data read from N consecutive register addresses, starting at ADDR     |

Via a burst mode, it is possible to write/read multiple consecutive register addresses with a single address upload.

The state of SPI\_CLK whenever SPI\_CSN is high is ignored, though it is advised to stop the clock to save unnecessary power consumption.

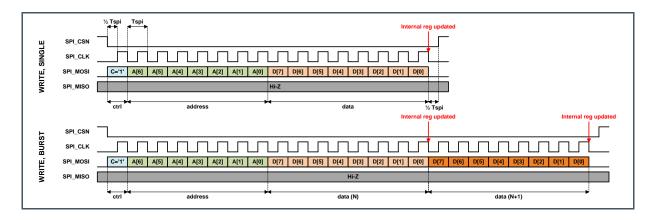

#### **SPI Write**

All data bits on SPI\_MOSI are sampled by the sensor on the rising edge of SPI\_CLK. The chip-select signal, SPI\_CSN, shall be low at least ½ of an SPI\_CLK period before the first data bit is sampled. SPI\_CSN shall remain low for at least ½ of an SPI\_CLK period after the last falling edge of SPI\_CLK. The first bit transferred is a control bit indicating a write operation ('1'). Both the subsequent address (A<6:0>) and data (D<7:0>) are sent MSB-first.

When writing multiple sequential registers (e.g. 100, 101, 102 ...), the write burst mode can be used. The address is that of the first register to be written to and the sequencer will automatically shift to the next register after 8 data bits. SPI\_CSN shall stay low the entire time.

The actual register value is updated with the new value on the falling edge of SPI\_CLK on every D[0] bit. I.e. SPI\_CLK shall go low at the end of D[0] for the write sequence to be completed. The timing of both write modes is illustrated below.

Figure 21: SPI Write Timing

#### **SPI Read**

The timing of the SPI read sequence is similar to the SPI write sequence. The main differences are the control bit and the use of SPI\_MISO. An SPI read is indicated by setting the control bit to '0'. After the control bit, the address of the register to read shall be transmitted MSB first. At the end of the LSB of the address, the data is launched on the SPI\_MISO pin on the falling edge of the SPI\_CLK. This means that the data can be sampled by the SPI master on the rising edge of the SPI\_CLK. The data D<7:0> is transmitted MSB first on SPI\_MISO. When not transmitting data, the SPI\_MISO output is in high-Z state.

Sequential SPI register addresses can also be read out in burst mode by keeping SPI\_CSN low and clocking out additional bytes. The timing of both read modes is illustrated below.

Figure 22: SPI Read Timing

#### **Register Banks**

The sensor's configuration registers are organized in five banks. Each bank contains 124, 8-bit registers.

To select a certain register bank, the register at address 0 is used. Address 0 is always accessible, regardless of the currently selected register bank.

Figure 23: Bank Selection Register

| Register Name | Bit Name | Bank | Addr | Pos   | Description |

|---------------|----------|------|------|-------|-------------|

|               |          |      |      |       | 0: Bank 0   |

|               |          |      |      |       | 1: Bank 1   |

| BANK_SEL      | BANK_SEL | N/A  | 0    | [2:0] | 2: Bank 2   |

|               |          |      |      |       | 3: Bank 3   |

|               |          |      |      |       | 4: Bank 4   |

The value of BANK\_SEL selects which register bank the current SPI access will have an effect on.

#### The Block ID

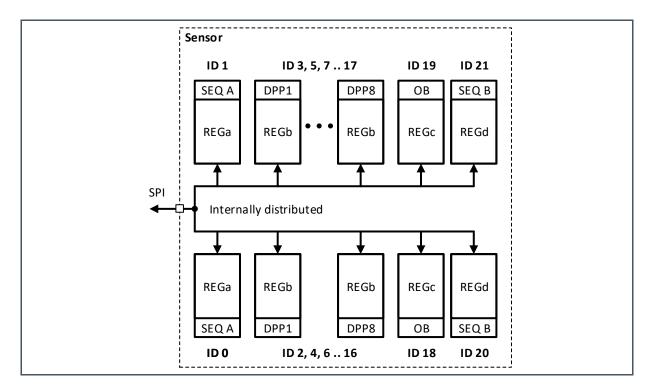

Inside the sensor, there are different blocks that each hold a unique copy of the register banks. The different blocks are the sequencers (A and B) and the DPPs for the output channels (VIS + OB). All of these blocks are connected to the SPI interface and are addressed with a unique identifier called the BLOCK\_ID.

Figure 26 shows the organization of all blocks in the sensor along with their BLOCK IDs. The sensor's SPI interface is distributed internally towards all blocks.

The BLOCK\_SEL register, located at address 1, determines which block is accessed by future SPI transactions. For example, when the BLOCK\_SEL register is set to 0, all SPI read and write operations act on the bottom sequencer A (which has BLOCK\_ID 0). The BLOCK\_SEL register is always accessible, regardless of the currently selected bank.

Figure 24: The BLOCK ID

The different blocks contain a certain subset of the total register bank, meaning that not every register is present in every block. This is denoted with REGa, REGb, REGc, and REGd in the figure above. Section 8 gives an overview of all registers that are included in every block.

A register (on a specific address) is always present in at least one block. If the register is present in multiple blocks, then each block hold a unique copy of that register, allowing it to be programmed differently in each of these blocks.

The sensor supports a broadcast mode where all blocks are written at once. This is done by setting the BLOCK\_SEL register to 255. This allows faster configuration as not every block has to be programmed individually. Blocks that do not contain the currently addressed register ignore the write operation, i.e. broadcasting does not overwrite anything in blocks that do not have the currently addressed register.

Registers are unique per address. This means that a register (with a certain name) is present on the same address in all blocks that contain this register. For blocks that do not contain this register, the address points to nothing. In this case, write operations are ignored and read operations return all zeros.

#### Information

SPI read operations in broadcast mode are not supported. The sensor will always return 0 whenever a register is read with BLOCK\_SEL set to 255.

SPI read operations can only be performed on single blocks.

Figure 25: Block Selection Register

| Register Name | Bit Name   | Bank | Addr | Pos   | Description                                                                        |

|---------------|------------|------|------|-------|------------------------------------------------------------------------------------|

|               |            |      |      |       | <ul><li>255: Broadcast (write access only)</li><li>0: Bottom sequencer A</li></ul> |

|               |            |      |      |       | 1: Top sequencer A                                                                 |

|               |            |      |      |       | 2: Bottom data channel 1                                                           |

|               |            |      |      |       | 3: Top data channel 1                                                              |

|               |            |      |      |       | 4: Bottom data channel 2                                                           |

|               |            |      |      |       | 5: Top data channel 2                                                              |

|               |            |      | 1    |       | 6: Bottom data channel 3                                                           |

|               |            |      |      |       | 7: Top data channel 3                                                              |

|               |            |      |      |       | 8: Bottom data channel 4                                                           |

|               |            |      |      | [7:0] | 9: Top data channel 4                                                              |

| BLOCK_SEL     | BLOCK_SEL  | N/A  |      |       | 10: Bottom data channel 5                                                          |

| 2200022       | 2200.12022 |      |      |       | 11: Top data channel 5                                                             |

|               |            |      |      |       | 12: Bottom data channel 6                                                          |

|               |            |      |      |       | 13: Top data channel 6                                                             |

|               |            |      |      |       | 14: Bottom data channel 7                                                          |

|               |            |      |      |       | 15: Top data channel 7                                                             |

|               |            |      |      |       | 16: Bottom data channel 8                                                          |

|               |            |      |      |       | 17: Top data channel 8                                                             |

|               |            |      |      |       | 18: Bottom OB channel                                                              |

|               |            |      |      |       | 19: Top OB channel                                                                 |

|               |            |      |      |       | 20: Bottom sequencer B                                                             |

|               |            |      |      |       | 21: Top sequencer B                                                                |

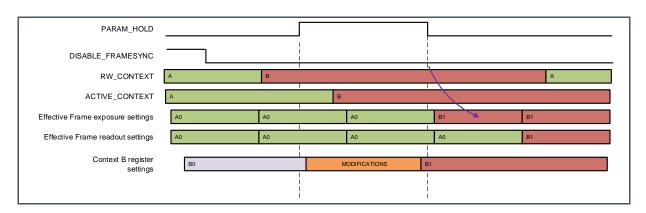

#### **Active Context Switching**

Selected registers related to exposure and readout can be set to define two different modes of operation or contexts. The register RW\_CONTEXT selects which context is accessed by the SPI interface for reading or writing.

Contexts can be switched quickly by a single access to the register ACTIVE\_CONTEXT. The sensor allows "on-the-fly" context switching, i.e. during any phase of the image acquisition, and will produce consistent images in terms of exposure and readout settings combinations.

Both RW\_CONTEXT and ACTIVE\_CONTEXT registers are always accessible, regardless of the currently selected bank.

Figure 26: Context Switching Registers

| Register Name     | Bank | Addr | Pos   | Description                                                                    |

|-------------------|------|------|-------|--------------------------------------------------------------------------------|

| ACTIVE_CONTEXT    | N/A  | 2    | [7:0] | 0: Use context A<br>1: Use context B                                           |

| RW_CONTEXT        | N/A  | 3    | [7:0] | 0: Access context A 1: Access context B                                        |

| PARAM_HOLD        | 0    | 4    | [0:0] | Must be set to '1' during the new context upload. See detailed procedure below |

| DISABLE_FRAMESYNC | 0    | 5    | [0:0] | Must be set to '0' for on-<br>the-fly context switching.                       |

The figure below shows how to upload a new context B and achieve a seamless context switch from context A to context B while acquiring frames (for example in streaming mode).

Figure 27 : Context Switch Procedure

- (1) DISABLE\_FRAMESYNC must be set to '0' first to guarantee uninterrupted frame acquisition

- (2) Then set RW\_CONTEXT to the inactive context (B in this example)

- (3) Set PARAM\_HOLD to '1', followed by all modifications to context B registers.

- (4) The setting of the new ACTIVE\_CONTEXT can be done at any time, while PARAM\_HOLD is '1'

- (5) When all uploads to context B are done, setting PARAM\_HOLD back to '0' will initiate a new frame using the exposure settings of context B, at the first frame time possible, while finishing the readout of the last frame with context A settings in parallel.

#### **Register Categories**

The registers are grouped into various categories, based on when they may or may not be updated. The category for every individual register can be found in section 8. The table below explains the details of the various categories.

Figure 28: Register Categories

| Category | Description                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -        | Registers without category can be changed at any time, but might directly influence the sensor execution.                                                                                                               |

| SYNC     | Registers are internally synchronized to start of frame (at the start of the GLOB state), so an entire frame is always read with the same SYNC configuration. This means that the registers may be updated at any time. |

| CONTEXT  | Registers can only be changed in the non-active context (i.e. RW_CONTEXT differs from ACTIVE_CONTEXT). These register can also be changed under the same conditions as DC, if ACTIVE_CONTEXT is the same as RW_CONTEXT. |

| DC       | Can only be changed when sensor is in IDLE state, or in soft reset state.                                                                                                                                               |

| RST      | Only to be changed when sensor is in soft reset state.                                                                                                                                                                  |

| RO       | Read-only register. All write operations are ignored.                                                                                                                                                                   |

Reading from a register is always allowed. When reading registers of category 'SYNC', the last value that was written to the register is read. The value read may differ from the value that the sensor's logic is currently using, as SYNC registers are frame-synchronized.

Figure 29: Frame Sync

| Reg. Name         | Bank | Addr | Bits | Def. | Description                                                               |

|-------------------|------|------|------|------|---------------------------------------------------------------------------|

| DISABLE_FRAMESYNC | 0    | 5    | [0]  | 0    | 0: Enable<br>1: Disable                                                   |

| PARAM_HOLD        | 0    | 4    | [0]  | 0    | Registers are frame synchronized     Registers are not frame synchronized |

The upload of 'SYNC' type registers can be constrained with the following registers:

If **DISABLE\_FRAMESYNC** is set to '1', frame synchronization is disabled. Any uploads will take effect immediately.

Frame synchronization only happens if **PARAM\_HOLD** is '0'. When uploading a bunch of SYNC-type registers together (for example, change a number of different YWIN settings), it is advised to set **PARAM\_HOLD** to '1' during the entire upload. This prevents a frame from being started with only half of the required updates in case the frame start happened when the entire upload had not completed.

#### 7.2.5 Soft Reset

Figure 30: Soft Reset Register

| Reg.Name                | В | Addr | Bits | Description                                                                                                   |

|-------------------------|---|------|------|---------------------------------------------------------------------------------------------------------------|

| CMD_REGS.CMD_RST_SOFT_N | 0 | 6    | [0]  | <ul><li>0: Soft-reset active (brings the sensor in soft-reset state)</li><li>1: Soft-reset inactive</li></ul> |

The sensor has an asynchronous reset input pin (RST\_N) and an asynchronous reset register (CMD\_RST\_SOFT\_N). Both are active-low.

When combined, they have the following function:

- RST\_N: Reset the entire sensor when low. This is considered a hard reset.

- CMD\_RST\_SOFT\_N: Reset the entire sensor, except the SPI interface and register bank when low. This is considered a soft reset.

As long as RST\_N is high, all registers retain their value when CMD\_RST\_SOFT\_N is low.

The procedures to assert and release soft reset are described in detail in section **7.4.3**.

#### 7.2.6 Controlling Exposure and Readout

This section explains the different ways the exposure of a frame can be started and ended. First some important concepts of the frame timing model are explained.

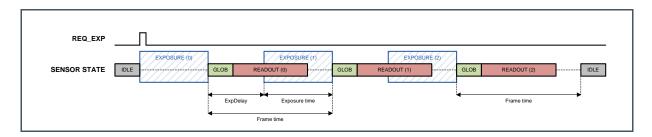

#### **Basic Frame Timing**

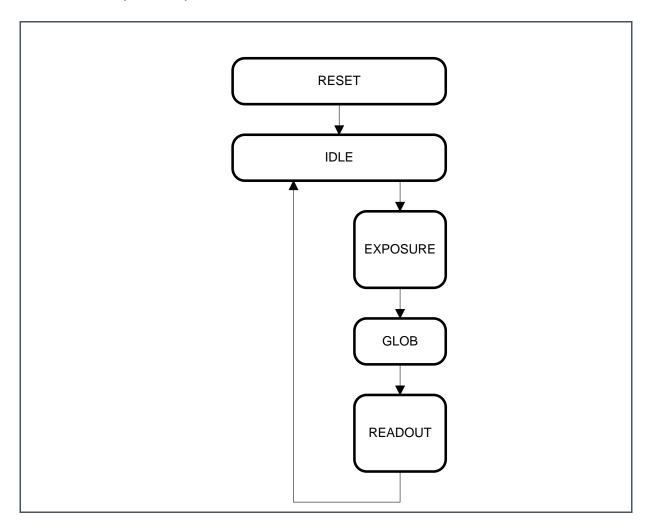

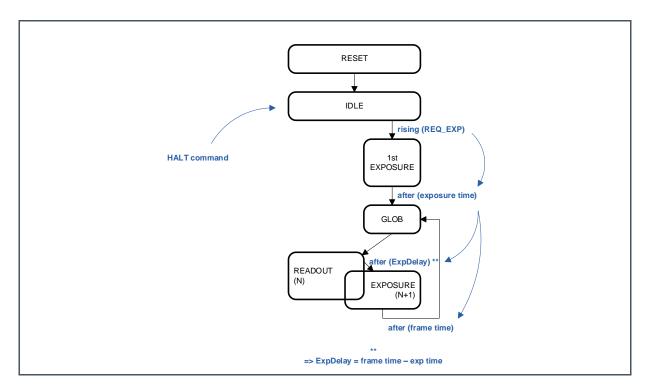

During operation, the sensor can be in any of the following states:

- RESET: Asynchronous sensor reset is low, disabling the sensor entirely

- IDLE: Sensor is not doing anything while waiting for external requests

- EXPOSURE: Light is being integrated in the pixels

- GLOB: Closing global shutter by sampling all integrated pixel values

- READOUT: Reading out the acquired frame plus meta data and mandatory overhead

A distinction can be made between two basic frame timing operations (sequential and pipelined operation), as detailed in the following two sections.

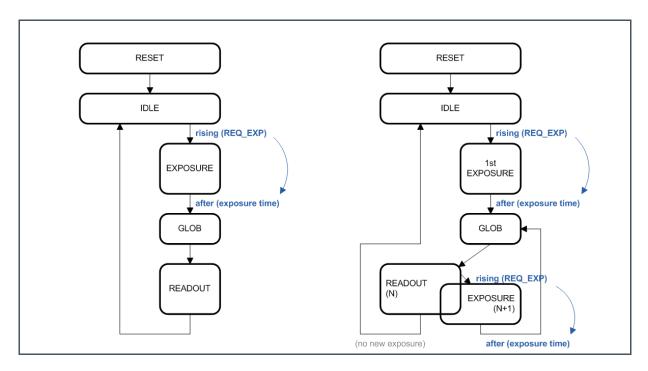

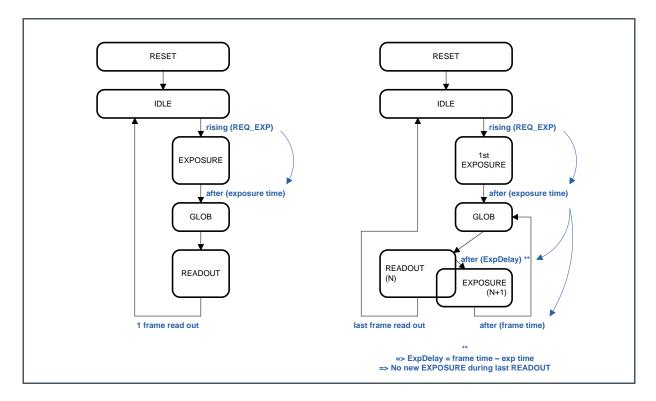

#### **Sequential Operation**

In sequential operation, the sensor goes through a sequential succession of EXPOSURE - GLOB - READOUT to grab a single image, as indicated in the figure below. When a cycle like this has been completed, the sensor is again in an IDLE state, waiting for new commands.

Figure 31:

**State Chart: Sequential Operation**

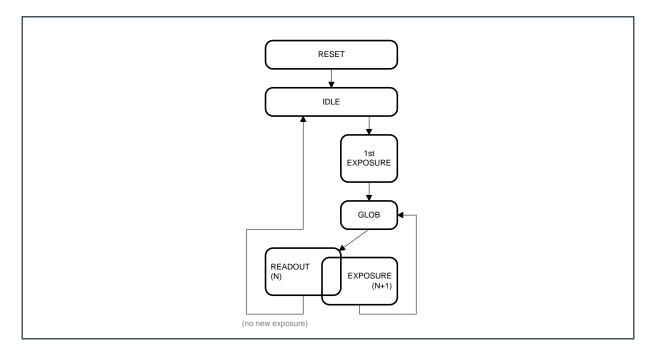

#### **Pipelined Operation**

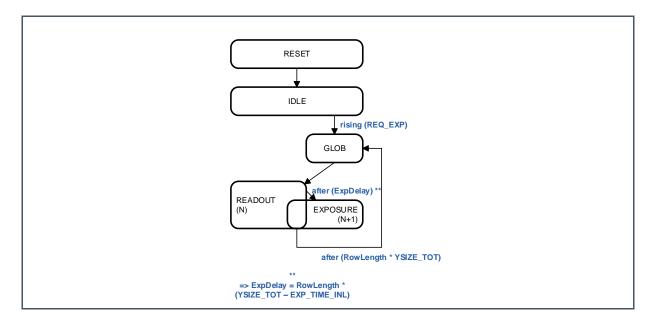

The main property of pipelined operation is that the sensor can be in the EXPOSURE state and READOUT state at the same time. This basically means that the readout of frame N can be busy while the EXPOSURE state of frame N+1 has already started. The EXPOSURE can fully or partially overlap with a READOUT state.

Figure 32:

**State Chart: Pipelined Operation**

When exiting IDLE state, the first EXPOSURE period starts. Just like in the sequential operation, this flows into a GLOB state, which in its turn starts the READOUT of a frame. Depending on the sensor control or configuration (see 7.2.7 for details and options), a new EXPOSURE may start when the READOUT is still busy.

At the end of the READOUT period, there are two options:

- No new EXPOSURE got started. The sensor will return to IDLE.

- A new EXPOSURE did get started. The sensor will wait until this new EXPOSURE finishes, before moving back to GLOB, which will always trigger a new READOUT.

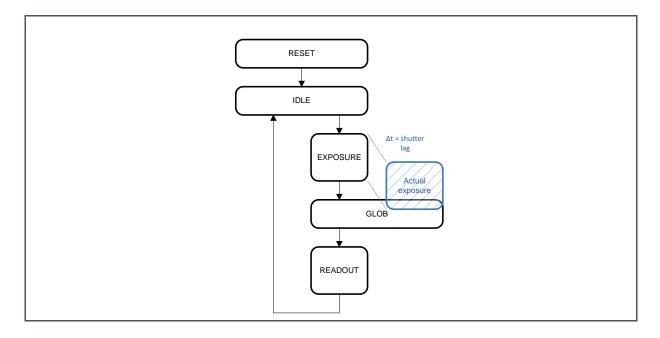

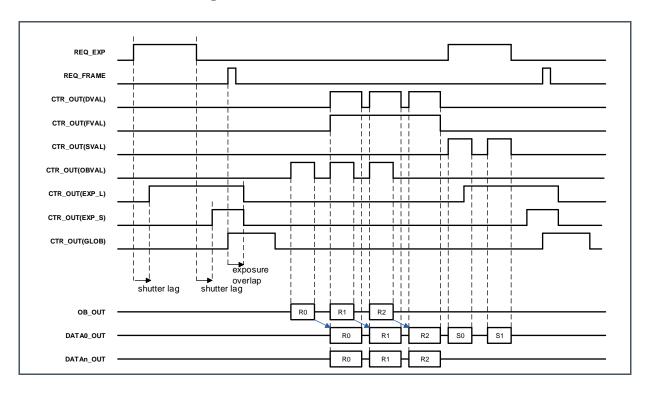

#### **Shutter Lag**

The shutter lag is the delay between the start and end of the **EXPOSURE state** and the start and end of the **actual exposure**. The actual exposure is the time where the sensor is actually capturing and integrating light. Figure 33 illustrates the shutter lag.

Figure 33: State Diagram: Sequential Operation with Shutter Lag

The distinction is important because the EXPOSURE state is the direct response of external control (through sensor I/O requests or register settings), but it is the actual exposure that really matters to the user.

In the remainder of the document, when the concept of exposure or exposure time is mentioned, it will always be about the **EXPOSURE state**, unless stated otherwise. The reader should always bear in mind that the **actual exposure** is delayed in time with respect to this EXPOSURE state due to the shutter lag mechanism.

In Figure 33, the shutter lag is shown under sequential operating conditions only, but note that the shutter lag is present in all operation modes.

The shutter lag is always present at the end of the EXPOSURE period, since part of the actual exposure time will always extend into the GLOB state. This is sometimes called "exposure overlap". The shutter lag at the beginning of the EXPOSURE periods is introduced artificially to compensate for this exposure overlap.

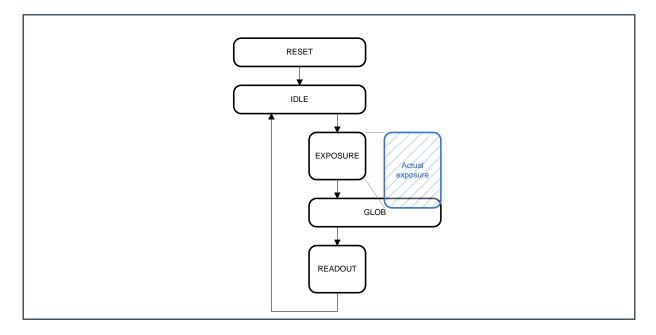

The shutter lag matching can also be disabled to operate in "no shutter lag"-mode. In that case, the sensor will move to the exposure state after a maximum internal latency of 33 \* t<sub>CLK\_PIX</sub> when it receives an exposure request. The start of the actual exposure happens together with the start of the exposure state. As a result, the length of the actual exposure time is larger than the length of the EXPOSURE state (the exposure overlap is added). Figure 34 shows the state diagram with the no shutter lag.

#### Information

Disabling shutter lag matching causes an image artefact when operating the sensor in pipelined mode. This artefact shows up as one bright row in the output image. The location of that row depends on when the pipelined exposure started.

Figure 34: State Diagram: Sequential Operation, No Shutter Lag at Start

#### 7.2.7 Sensor Control Modes

Figure 35: Control Mode Register

| Reg.Name  | Bank | Addr | Bits  | Def. | Description                                                                                         |

|-----------|------|------|-------|------|-----------------------------------------------------------------------------------------------------|

| CTRL_MODE | 0    | 11   | [2:0] | 0    | O: Full external  1: Programmed external  2: Triggered internal  3: Streaming  4: In-line streaming |

The travel through the state diagrams of Figure 33 and Figure 34 can be externally controlled with the sensor inputs REQ\_EXP and REQ\_FRAME and a bunch of register settings (which will be detailed in further sections). This can be done in a number of different modes (each varying slightly in behavior and level of dependency on I/O control versus register configuration).

The control mode is set with the CTRL\_MODE register, as listed in Figure 36.

Figure 36: Control Modes

| CTRL MODE | Name                             | External Control                                       | Internal Control                                                  |

|-----------|----------------------------------|--------------------------------------------------------|-------------------------------------------------------------------|

| 0         | Full external                    | Start of exposure. End of exposure (starting readout). | Readout details.                                                  |

| 1         | Programmed external              | Start of exposure.                                     | Length of exposure. Readout details.                              |

| 2         | Triggered internal               | A finite sequence of 1 or more consecutive frames.     | Length of exposure. Frame rate. Sequence length. Readout details. |

| 3         | Streaming                        | An infinite sequence of consecutive frames.            | Length of exposure. Frame rate. Readout details.                  |

| 4         | In-line streaming <sup>(1)</sup> |                                                        |                                                                   |

(1) The in-line streaming mode is a special case, dedicated to readout with very small window sizes for "line scan"-like applications. As it differs quite a lot from the other control modes, it is only mentioned here for completeness' sake and will be further detailed in section 7.8.2.

Each of these control modes is introduced in one of the following sections.

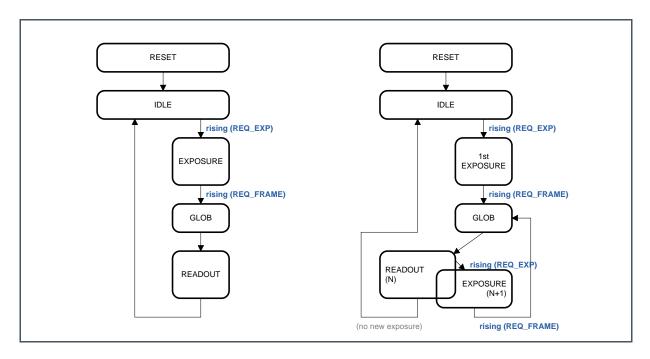

#### Control Mode 0: Full External

In the Full External control mode, the exposure timing is fully controlled with the sensor input pins:

- A rising edge on REQ\_EXP moves the sensor to the EXPOSURE state

- A rising edge on REQ\_FRAME moves the sensor to the GLOB state, which will be automatically followed by READOUT.

The length of the EXPOSURE state will exactly match the time between the rising edges of both triggers.

In the figure below, the state diagrams of sequential and pipelined operation are annotated with the external control events.

Figure 37:

State Diagram: Full External Mode

The length of the GLOB state, as well as the length of the READOUT period depends on a number of register settings.

The state diagram is expanded into a timing diagram for a few situations in the figure below.

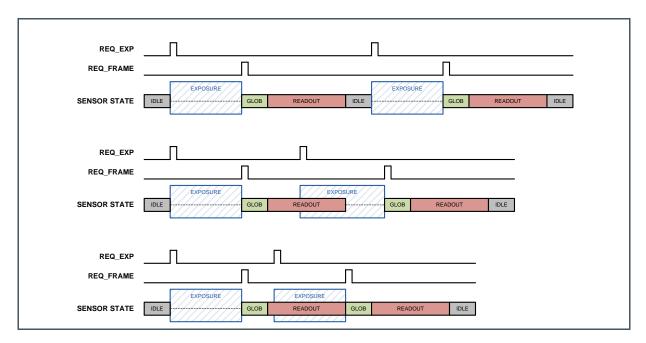

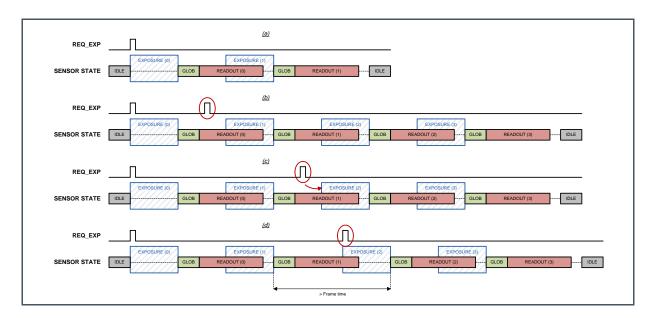

Figure 38: Timing Diagram: Full External Mode

The figure shows how the Full External control mode can be used to (from top to bottom):

- Operate the sensor in Sequential Operation mode.

- Operate the sensor in *Pipelined Operation* mode, with the parallel exposure extending beyond the readout phase.

- Operate the sensor in *Pipelined Operation* mode, with the parallel exposure ending together with the readout phase (gives maximum frame rate).

Except for the invalid timings listed in Figure 39 the requests on REQ\_EXP and REQ\_FRAME can be freely placed anywhere by the external controller. This will result in the most flexible external control possible with this sensor (start and end exposure at any possible time, freely vary exposure time from frame to frame, interrupt frames being read to start a new readout).

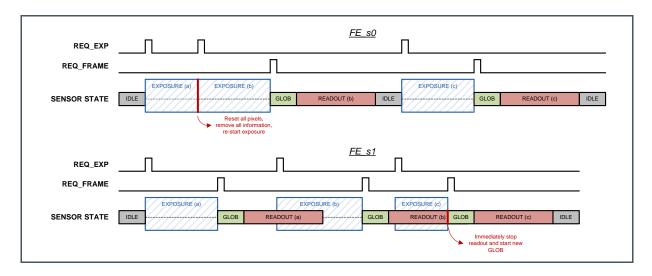

Figure 39: Full External Mode: Invalid Control Timing

| #     | Invalid Control Timing                              | Sensor Response                                                                                                                                 |

|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| FE_i0 | REQ_EXP during GLOB                                 | Will disrupt the GLOB execution, causing the READOUT that naturally follows the GLOB phase to contain corrupted data.                           |

| FE_i1 | REQ_FRAME during GLOB                               | Will initiate a new GLOB, followed by READOUT. Image data in this READOUT will be corrupt.                                                      |

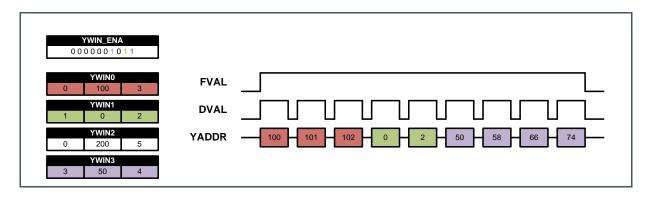

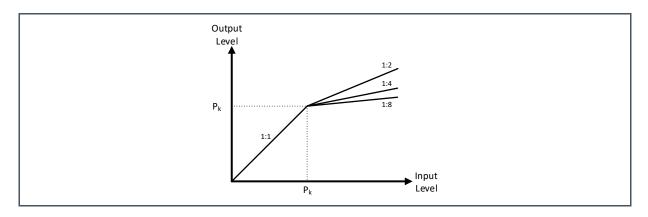

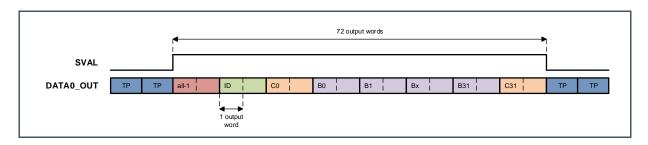

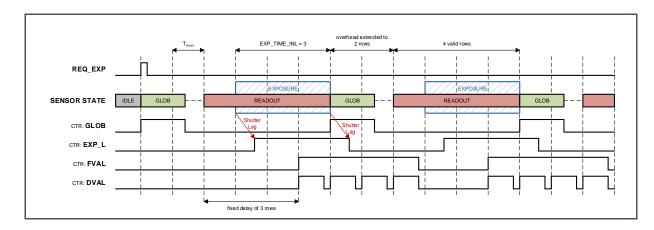

| FE_i2 | 2 consecutive REQ_FRAME, without REQ_EXP in between | Second REQ_FRAME will initiate GLOB followed by READOUT. Since there has not been EXPOSURE, the image data in the second frame will be corrupt. |