# **NSSHNBO**

# RN5T5611-xx-E4 Series AEC-Q100 Compliant

# Programmable Power Management IC for Automotive Applications

## OVERVIEW

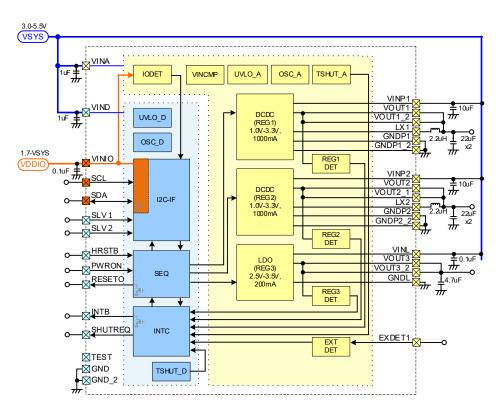

The RN5T5611 is a power management IC (PMIC) for automotive applications. This IC provides two highefficiency step-down DCDC converters, a low-noise regulator, an interrupt controller (INTC), and I<sup>2</sup>C-bus interface. Power-supply start and stop sequences can be customized to meet user-system. In addition to the basic power control, this IC provides various protection functions.

## **KEY BENEFITS**

- Compliance with ASIL-D

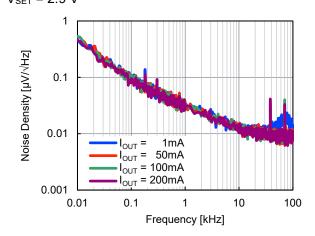

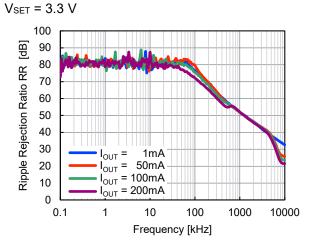

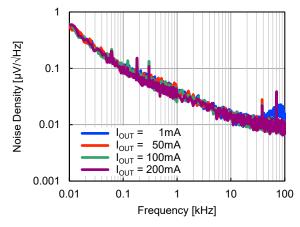

- LDO regulator is provides low output noise, high ripple rejection and fast response characteristics.

- Flexible selection such as sequence and enable simplifies power sequence control.

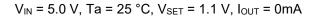

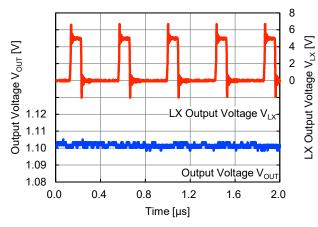

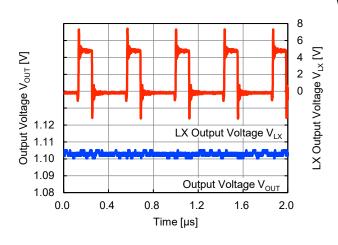

- 2ch Step-down DCDC converters operate with 180° turn-on phase shift of the switching transistors.

KEY SPECIFICATIONS

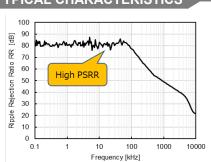

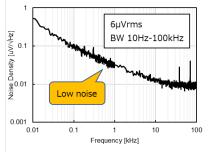

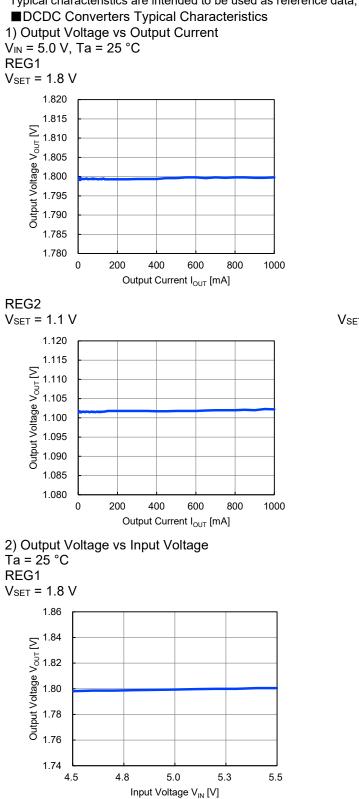

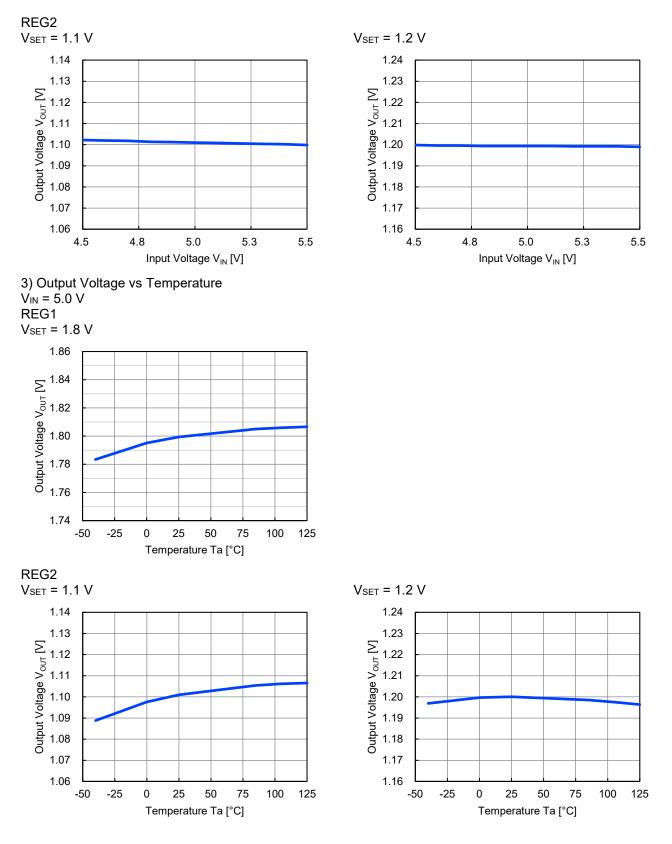

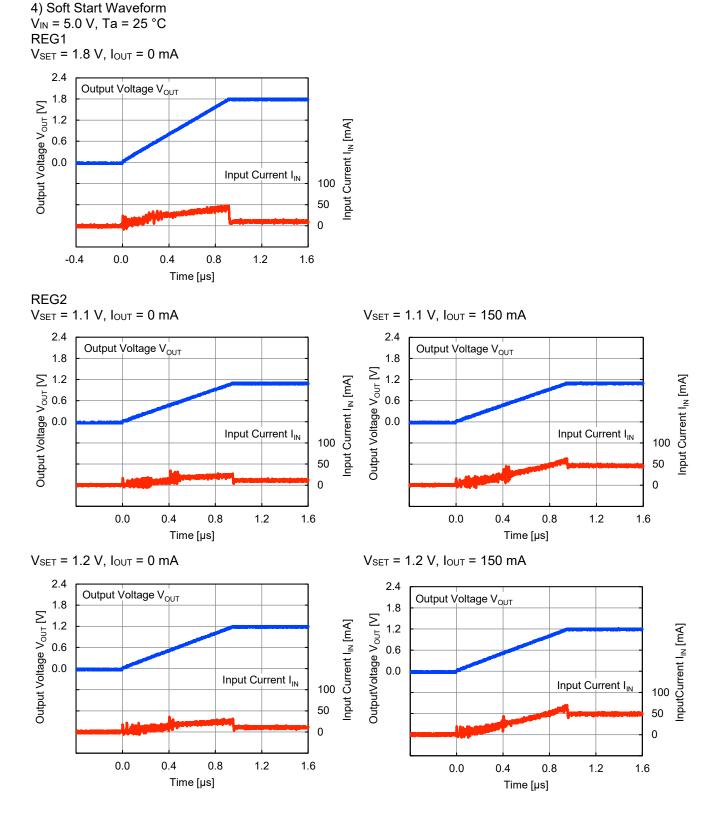

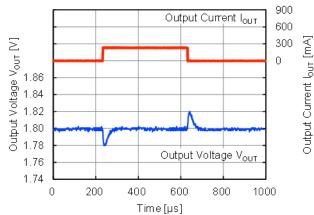

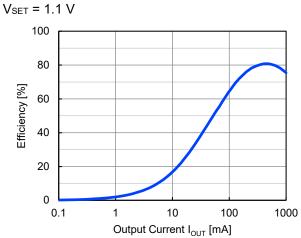

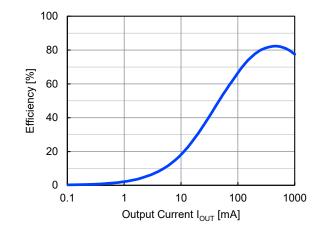

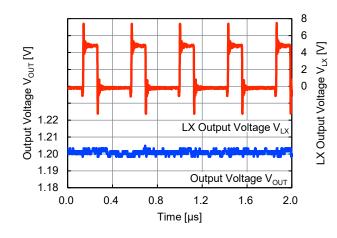

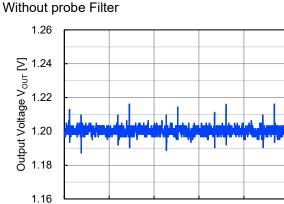

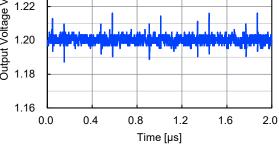

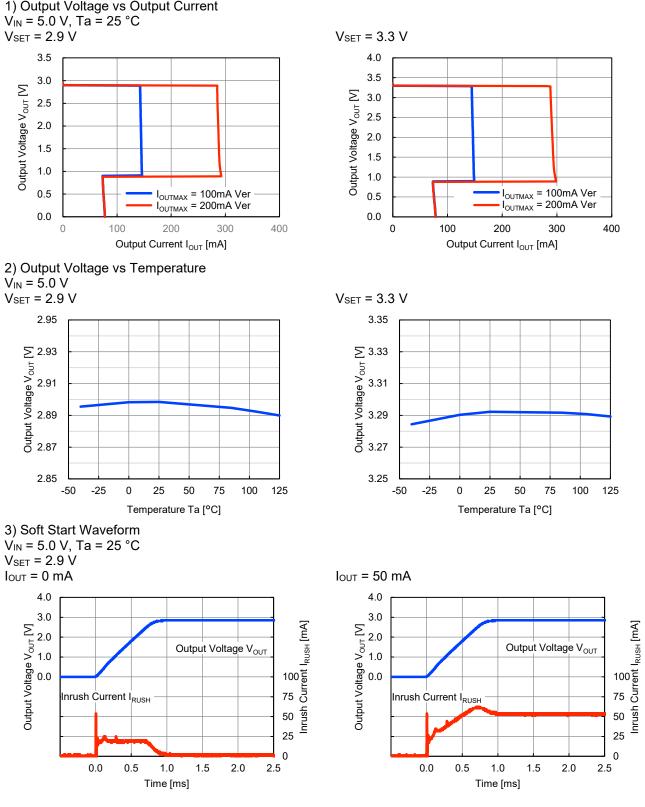

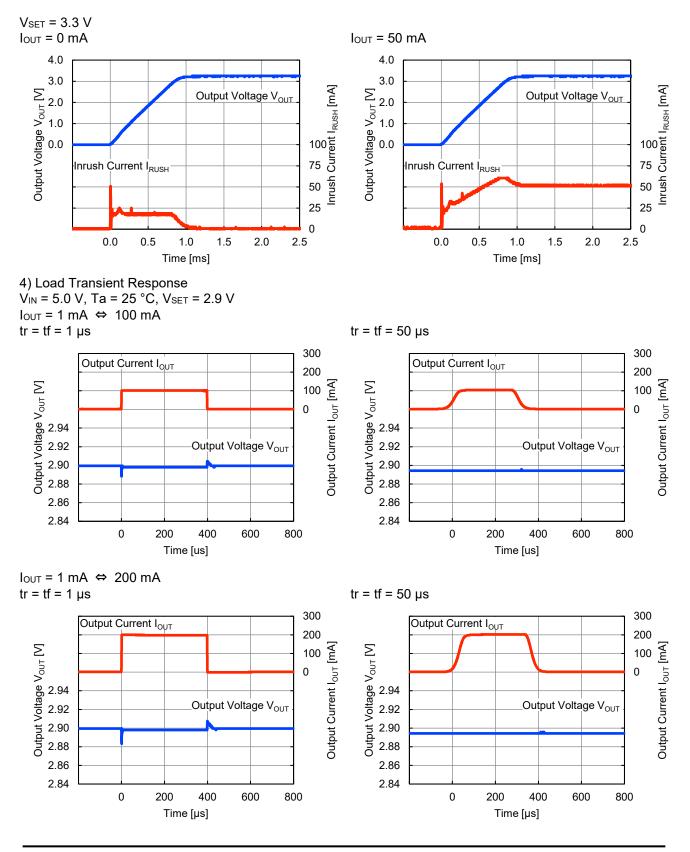

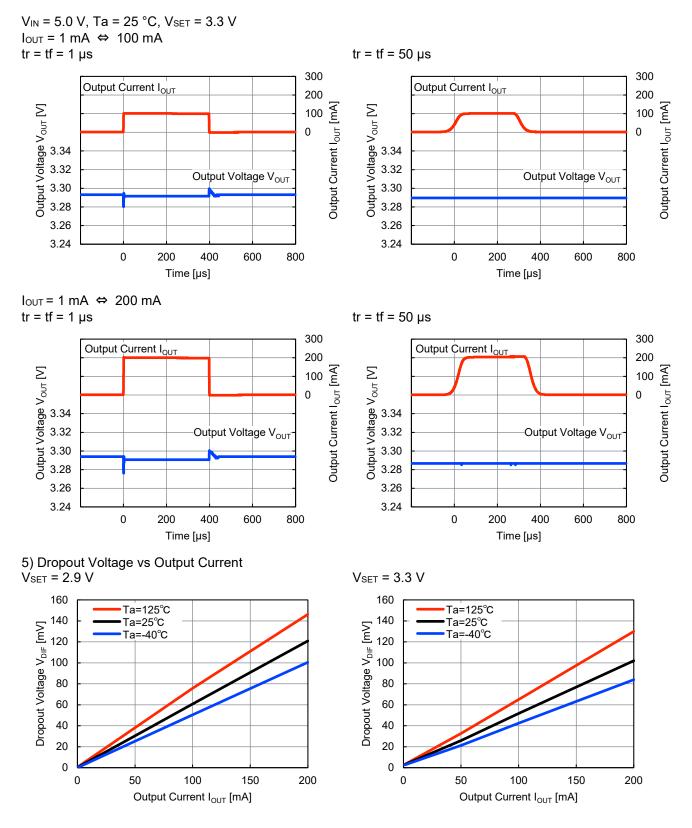

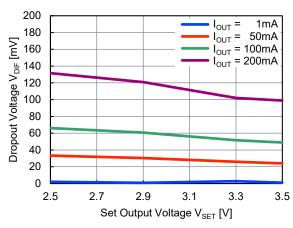

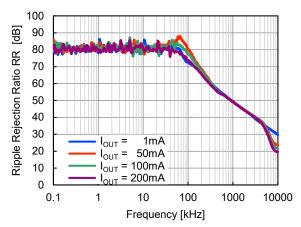

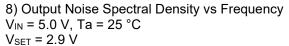

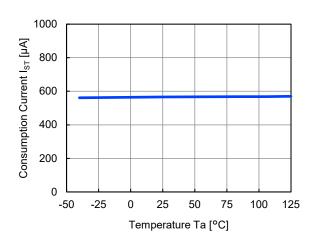

TYPICAL CHARACTERISTICS

- Input Voltage Range (Maximum Ratings): 3.0 V to 5.5V<sup>(1)</sup> (6.5V)

- Operating Temperature Range: -40°C to 125°C

- High Efficiency Step-down DCDC Converters (REG1,2)

- Output Range: 1.0 V to 3.3 V ±1% (Max. 1.0A)

- Oscillator Frequency: 2.3MHz

- Operating Mode: Forced PWM Mode

- Overcurrent / Reverse Current Protection (Latch)

- Low Drop Voltage Regulator (REG3: Low Output Noise)

- Output Range: 2.5 V to 3.5 V ±1% (Max. 200mA)

- Output Noise: Typ. 6 µVrms (I<sub>OUT</sub> = 100 mA)

- PSRR: Typ. 80 dB (@1 kHz), Typ. 80 dB (@100 kHz)

- Short Circuit Protection

- I<sup>2</sup>C-bus Interface: 1MHz and 400kHz

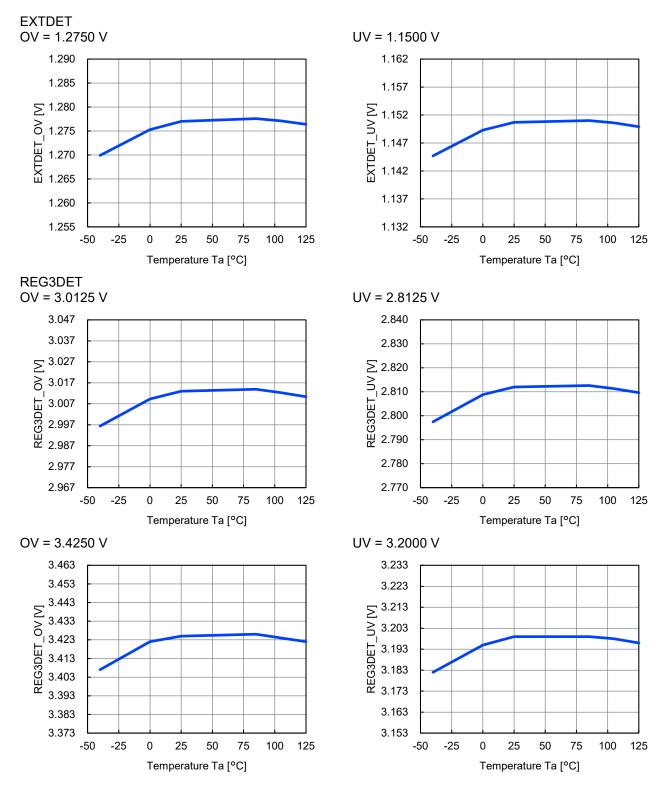

- Window Voltage Detector for Internal DCDC (REG1,2), LDO (REG3) and External pin

- REG1/2DET: OV/UV 0.6V to 3.7V (12.5mV Step)  $\pm$  1%  $^{(2)}$

- REG3DET: OV/UV 2.0V to 4.0V (12.5mV Step) ± 1%

- EXTDET: OV/UV 0.6V to 3.7V (12.5mV Step) ± 1% (2)

- UVLO (Under Voltage Lock Out)

- Soft-start Circuit

- Auto-discharge

- Switching Phase Shift (DCDC)

- Flexible Setting (Output/Sequence/REG's Reaction to Errors)

- Status Monitoring by Built-in Registers

- Error Output by Interrupt Signal

- Forced Power Off by HRSTB pin

- Thermal Shutdown: Tj = 165°C

#### APPLICATIONS

• ADAS including Front sensing system, Camera monitoring system, Surround view, etc.

$^{(1)}$  The recommended operating voltage range is specified by the product code  $^{(2)}$  ± 1.3% at OV/UV < 1 V

Nisshinbo Micro Devices Inc.

No.EC-622-220627

PSRR (V<sub>IN</sub> = 5.0 V, V<sub>OUT</sub> = 2.9 V)

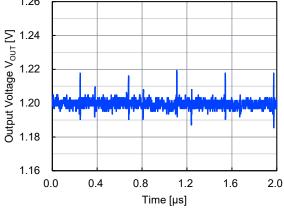

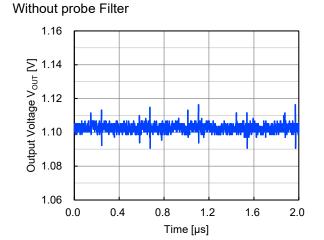

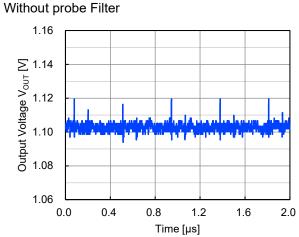

Output Noise (I<sub>OUT</sub> = 100 mA)

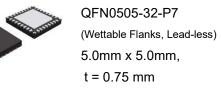

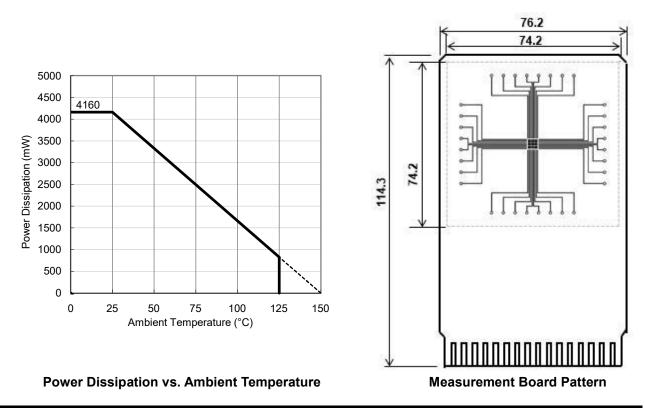

PACKAGE

nagement is for Automotive A

No.EC-622-220627

## **SELECTION GUIDE**

#### **Selection Guide**

| Product Name      | Package       | Quantity per Reel | Pb Free | Halogen Free |

|-------------------|---------------|-------------------|---------|--------------|

| RN5T5611-xx-E4-#E | QFN0505-32-P7 | 1,000 pcs         | Yes     | Yes          |

xx: Specify a product code. Refer to Appendix "Product Code List" for details.

#### #: Quality Class

|   | Operating Temp. Range | Test Temp.      |  |  |  |

|---|-----------------------|-----------------|--|--|--|

| К | −40°C to 125°C        | Low, 25°C, High |  |  |  |

## **BLOCK DIAGRAM**

**RN5T5611 Block Diagram**

# Nisshinbo Micro Devices Inc.

No.EC-622-220627

# **PIN DESCRIPTION**

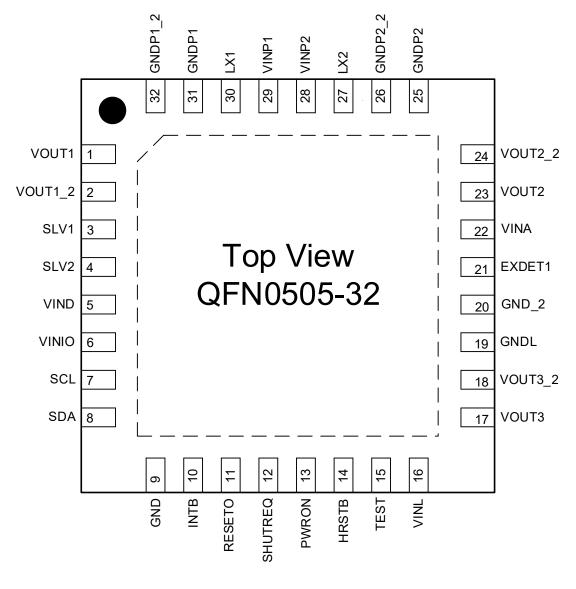

**RN5T5611** Pin Configuration

No.EC-622-220627

## **Pin Assignments**

| No. | Pin Name | Function                                               |        | D/A <sup>(2)</sup> | Reset | State <sup>(3)</sup> | Note                            |

|-----|----------|--------------------------------------------------------|--------|--------------------|-------|----------------------|---------------------------------|

| NO. |          | Function                                               | 1/0(1/ | <b>D/A</b> (-/     | I/O   | Level                | NOLE                            |

| 1   | VOUT1    | REG1 output pin                                        | I/O    | А                  | _     | _                    |                                 |

| 2   | VOUT1_2  |                                                        |        |                    |       |                      |                                 |

| 3   | SLV1     | I <sup>2</sup> C-bus slave address [1(LSB)] select pin | I      | D                  | Ι     | -                    | CMOS Schmitt                    |

| 4   | SLV2     | l <sup>2</sup> C-bus slave address [2] select pin      | Ι      | D                  | Ι     | -                    | CMOS Schmitt                    |

| 5   | VIND     | Power supply for Digital                               | -      | Р                  | -     | -                    |                                 |

| 6   | VINIO    | Power supply for I <sup>2</sup> C-bus interface I/O    | -      | Р                  | -     | -                    |                                 |

| 7   | SCL      | l <sup>2</sup> C-bus input clock pin                   | Ι      | D                  | -     | -                    | CMOS Schmitt                    |

| 8   | SDA      | I <sup>2</sup> C bus data pin                          | I/O    | D                  | Ι     | Hi-z                 | CMOS Schmitt,<br>Nch Open Drain |

| 9   | GND      | GND for Analog and Digital circuits                    | -      | G                  | -     | -                    |                                 |

| 10  | INTB     | Interrupt pin                                          | 0      | D                  | 0     | Hi-z                 | Nch Open Drain <sup>(4)</sup>   |

| 11  | RESETO   | reset output pin                                       | I/O    | D                  | 0     | Low                  | Nch Open Drain <sup>(4)</sup>   |

| 12  | SHUTREQ  | Shut down Request                                      | 0      | D                  | 0     | Low                  | CMOS Output                     |

| 13  | PWRON    | Power On pin                                           | Ι      | D                  | -     | -                    | NMOS Schmitt (5)                |

| 14  | HRSTB    | Hardware reset input pin                               | Ι      | D                  | Ι     | -                    | NMOS Schmitt <sup>(5)</sup>     |

| 15  | TEST     | Test pin (Connect to GND)                              | Ι      | D                  | I     | -                    | CMOS Schmitt <sup>(5)</sup>     |

| 16  | VINL     | Power supply for REG3                                  | -      | Р                  | I     | -                    |                                 |

| 17  | VOUT3    | PEC2 output pip                                        | I/O    | А                  |       |                      |                                 |

| 18  | VOUT3_2  | REG3 output pin                                        | 1/0    | A                  | -     | -                    |                                 |

| 19  | GNDL     | GND for REG3                                           | -      | G                  | -     | -                    |                                 |

| 20  | GND_2    | GND for Analog and Digital circuits                    | -      | G                  | -     | -                    |                                 |

| 21  | EXDET1   | External input voltage detector sense pin              | Ι      | А                  | I     | -                    |                                 |

| 22  | VINA     | Power supply for Analog                                | -      | Р                  | I     | -                    |                                 |

| 23  | VOUT2    |                                                        | 1/0    | ^                  |       |                      |                                 |

| 24  | VOUT2_2  | REG2 output pin                                        | I/O    | A                  | -     | -                    |                                 |

| 25  | GNDP2    |                                                        |        | 0                  |       |                      |                                 |

| 26  | GNDP2_2  | GND for REG2                                           | -      | G                  | -     | -                    |                                 |

| 27  | LX2      | REG2 switching pin                                     | 0      | А                  | -     | -                    |                                 |

| 28  | VINP2    | Power supply for REG2                                  | -      | Р                  | -     | -                    |                                 |

| 29  | VINP1    | Power supply for REG1                                  | -      | Р                  | -     | -                    |                                 |

| 30  | LX1      | REG1 switching pin                                     | 0      | Α                  | -     | -                    |                                 |

| 31  | GNDP1    |                                                        |        | 6                  |       |                      |                                 |

| 32  | GNDP1_2  | GND for REG1                                           | -      | G                  | -     | -                    |                                 |

<sup>(1)</sup> I: Input, O: Output

<sup>(2)</sup> A: Analog, D: Digital, P: Power, G: Ground

<sup>(3)</sup> HRSTB pin is driven low.

$^{(4)}$  Require an external pull-up resistor of 10 k $\Omega$  to 100 k $\Omega.$

<sup>(5)</sup> With a built-in pull-down resistor

No.EC-622-220627

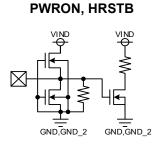

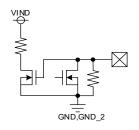

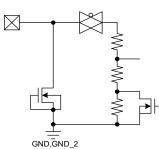

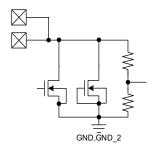

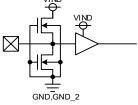

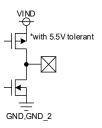

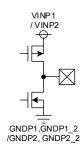

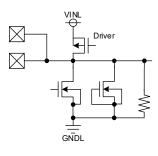

## **Equivalent Circuits for the Individual Pins**

SDA, SCL

INTB

TEST

VOUT1, VOUT1\_2

RESETO

VOUT2, VOUT2\_2

SLV1, SLV2

SHUTREQ

LX1, LX2

## VOUT3, VOUT3\_2

No.EC-622-220627

# **ABSOLUTE MAXIMUM RATINGS**

|         | $(GNDs^{(1)} = 0 V)$ |                                       |                                |    |  |  |  |  |  |  |

|---------|----------------------|---------------------------------------|--------------------------------|----|--|--|--|--|--|--|

| Symbol  | Parameter            | Condition                             | Condition Rating               |    |  |  |  |  |  |  |

|         | Dower Supply Voltage | VINA, VIND, VINIO, VINL               | -0.3 to 6.5                    | V  |  |  |  |  |  |  |

| Vps     | Power Supply Voltage | and VINP1-2 pins                      | -0.3 10 0.5                    | V  |  |  |  |  |  |  |

|         |                      | EXDET1 pin                            | –0.3 to V <sub>INA</sub> + 0.3 | V  |  |  |  |  |  |  |

| VINPUT  | Input Voltage Range  | PWRON, HRSTB and SLV1-2 pins          | –0.3 to V <sub>IND</sub> + 0.3 | V  |  |  |  |  |  |  |

|         |                      | SDA and SCL pins                      | –0.3 to 6.5                    | V  |  |  |  |  |  |  |

| Voutput | Output Voltage Range | SHUTREQ, INTB and RESETO pins         | –0.3 to V <sub>IND</sub> + 0.3 | V  |  |  |  |  |  |  |

| Tj      | Junction Temperature | -                                     | –40 to 150                     | °C |  |  |  |  |  |  |

| Tstg    | Storage Temperature  | -                                     | –55 to 150                     | °C |  |  |  |  |  |  |

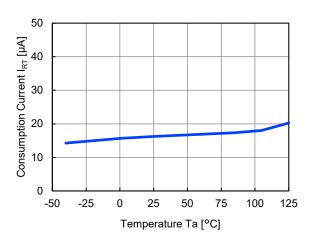

| PD      | Package Dissipation  | Refer to Appendix "Power Dissipation" |                                |    |  |  |  |  |  |  |

## ABSOLUTE MAXIMUM RATINGS

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the lifetime and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings are not assured.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol                      | Parameter            | Parameter Condition Mi                             |     | Тур.                         | Max.  | Unit |

|-----------------------------|----------------------|----------------------------------------------------|-----|------------------------------|-------|------|

| Vsys                        | Power Supply Voltage | Power Supply Voltage      VIN* pins (2)      × 0.9 |     | $V_{SYS_TYP}$ <sup>(4)</sup> | × 1.1 | V    |

| Vddio                       | Power Supply Voltage | VINIO pin <sup>(3)</sup>                           | 1.7 | 1.8                          | VIND  | V    |

| GND                         | Ground               | GNDs (1)                                           |     | 0                            |       | V    |

| Ta Temperature of Operation |                      | -                                                  | -40 |                              | 125   | °C   |

#### **RECOMMENDED OPERATING CONDITIONS**

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating ratings. The semiconductor devices cannot operate normally over the recommended operating ratings, even if they are used over such ratings by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating ratings.

<sup>(1)</sup> GNDs: GND signals including GND, GND\_2, GNDL, GNDP1, and GNDP2.

<sup>&</sup>lt;sup>(2)</sup> VINP1-2, VINL and VIND must be equal to VINA.

<sup>(3)</sup> VINIO must be less than or equal to VIND.

<sup>&</sup>lt;sup>(4)</sup> V<sub>SYS\_TYP</sub> is Specify the Product Code. Refer to "Product Code List" for details.

No.EC-622-220627

# **ELECTRICAL CHARACTERISTICS**

| O Electr        | ical Characteristics             |                        |                        | (–40 | 0°C ≤ Ta ≤ 1         | 125°C |

|-----------------|----------------------------------|------------------------|------------------------|------|----------------------|-------|

| Symbol          | Parameter                        | Condition              | Min.                   | Тур. | Max.                 | Unit  |

| /IND NMO        | S Input Pin (NMOS Schmitt): PWR  | ON, HRSTB              |                        |      |                      |       |

| VIL             | Low level input voltage          |                        |                        |      | 0.4                  | V     |

| VIH             | High level input voltage         |                        | 1.6                    |      | VIND                 | V     |

| I <sub>PD</sub> | Pull down current                | VIN = VIND             |                        |      | 2                    | μA    |

| lı∟             | Input Leakage Current            | VIN = 0V               | -1                     |      | 1                    | μA    |

| ND CMO          | S Input Pin (CMOS Schmitt): SLV1 | ,2                     |                        | 1    |                      |       |

| VIL             | Low level input voltage          |                        |                        |      | $V_{IND} \times 0.3$ | V     |

| VIH             | High level input voltage         |                        | V <sub>IND</sub> × 0.7 |      | VIND                 | V     |

| ND Nch (        | Open-drain Output Pin: INTB, RES | ETO                    |                        |      | •                    |       |

| Vol             | Low level output voltage         | I <sub>OUT</sub> = 2mA |                        |      | 0.4                  | V     |

| VTO             | Tolerant                         |                        |                        |      | VIND                 | V     |

| IND CMO         | S Output Pin: SHUTREQ            |                        |                        |      |                      |       |

| Vol             | Low-level Output Voltage         | Ι <sub>ουτ</sub> = 2mA |                        |      | 0.4                  | V     |

| Vон             | High-level Output Voltage        | Ιουτ = -2mA            | V <sub>IND</sub> – 0.4 |      |                      | V     |

| Symbol                                    | Parameter                          | Condition                 | Min.                    | Тур. | Max.                  | Unit |  |  |  |

|-------------------------------------------|------------------------------------|---------------------------|-------------------------|------|-----------------------|------|--|--|--|

| VINIO CMOS Input Pin (Schmitt Input): SCL |                                    |                           |                         |      |                       |      |  |  |  |

| VIL                                       | Low level input voltage            |                           |                         |      | $V_{INIO} \times 0.3$ | V    |  |  |  |

| VIH                                       | High level input voltage           |                           | V <sub>INIO</sub> × 0.7 |      | VINIO                 | V    |  |  |  |

| VINIO CMO                                 | S Input / Output Pin (Schmitt Inpu | nt / Nch Open-drain Outpu | ut): SDA                |      |                       |      |  |  |  |

| VIL                                       | Low level input voltage            |                           |                         |      | $V_{INIO} \times 0.3$ | V    |  |  |  |

| VIH                                       | High level input voltage           |                           | V <sub>INIO</sub> × 0.7 |      | VINIO                 | V    |  |  |  |

| Vol                                       | Low level output voltage           | I <sub>OUT</sub> = 20mA   |                         |      | 0.4                   | V    |  |  |  |

| Consumption Current <sup>(1)</sup> $(-40^{\circ}C \le Ta \le 125^{\circ})$ |                 |                             |  |      |      |      |  |

|----------------------------------------------------------------------------|-----------------|-----------------------------|--|------|------|------|--|

| Symbol                                                                     | Parameter       | Condition<br>(Device State) |  | Тур. | Max. | Unit |  |

| I <sub>RT</sub>                                                            | Reset current   | Reset                       |  |      | 40   | μA   |  |

| I <sub>ST</sub>                                                            | Standby current | Ready                       |  |      | 0.8  | mA   |  |

<sup>(1)</sup>  $V_{SYS} = V_{SYS_TYP}$  at No-load, unless otherwise specified.

No.EC-622-220627

# THEORY OF OPERATION

## **Power Control**

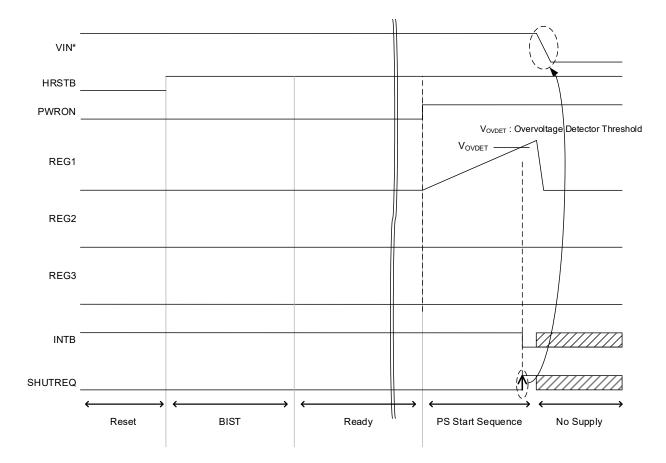

This IC has the start and stop sequences for the power supply.

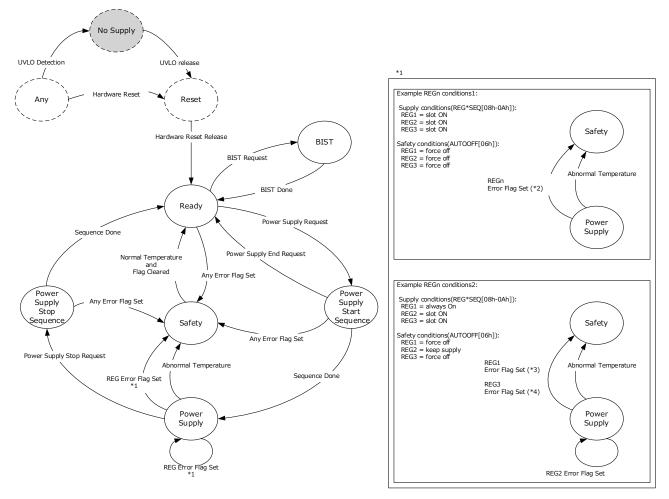

#### **State Machine Diagram**

Figure 1 State Machine Diagram

\*1 The transition after detecting an error is programmable.

\*<sup>2</sup> All REGs are turned off.

\*3 All REGs are turned off.

\*4 REG2 and REG3 are turned off. REG1 remains on.

Nisshinbo Micro Devices Inc.

No.EC-622-220627

#### **State Machine Description**

The state machine steps through the following states:

#### No Supply

This IC receives no power supply.

Transfer Conditions:

· If this IC detects a UVLO release, the state transitions to the Reset state.

#### <u>Reset</u>

Makes all regulators turn-off.

Initializes all register settings and makes it impossible to access through the I<sup>2</sup>C-bus interface.

Transfer Conditions:

• If the HRSTB pin is high, the state transitions to the Ready state.

## <u>Ready</u>

Makes all regulators ready for power supply. Makes always-on regulator turn-on and the other regulators turn-off. Makes it possible to access to the registers through the I<sup>2</sup>C-bus interface. <sup>(1)</sup>

Transfer Conditions:

- REGn voltage of always-on regulator reaches a target voltage.

- If the BISTEN bit is "1", the state transitions to the BIST state.

- If the Safety Mechanism (SM) detects an error, the state transitions to the Safety state.

- If the PWRON pin is "High", the state transitions to the PS Start Sequence state.

## BIST (Built-in self-test).

Executes Analog and Logic BIST and sets the results to registers.

Transfer Conditions:

• If the BISTEN bit becomes "0" by BIST, the state transitions to the Ready state.

## **Power Supply Start Sequence**

Makes each regulator turn-on sequentially.

Transfer Conditions:

- · If the SM detects an error, the state transitions to the Safety state.

- If each regulator is turned off immediately after the PWRON pin of "Low", the state transitions to the Ready state.

- If the sequence is finished, the state transitions to the Power Supply state.

<sup>&</sup>lt;sup>(1)</sup> The VINIO power input is required to access through the I<sup>2</sup>C-bus interface.

No.EC-622-220627

#### **Power Supply**

Makes each regulator turn-on. Makes it possible to access to the registers through the I<sup>2</sup>C-bus interface.<sup>(1)</sup>

Transfer Conditions:

- If the TSHUT detects an abnormal temperature, the state transitions to the Safety state.

- If the SM detects the regulator's overcurrent / reverse current, the state transitions to the Safety state.

- If the SM detects any regulator's under/over-voltage error, the state transitions to the Safety state in a case where the DISnAUTOOFF bits are all "0", the state transition remains in a case where the DISnAUTOOFF bits are all "1".

#### **Power Supply Stop Sequence**

Makes each regulator turn-off sequentially.

Transfer Conditions:

- · If the SM detects an error, the state transitions to the Safety state.

- If the sequence is finished, the state transitions to the Ready state.

#### <u>Safety</u>

Makes all regulators turn-off when the SM detects an error. But, if the always-on regulator only has not any errors, remains its regulator on.<sup>(2)</sup>

Makes it possible to access to the registers through the l<sup>2</sup>C-bus interface. It becomes able to read and clear the error flags.

Transfer Conditions:

When the number of the error detection is less than the number of the auto-restoration,

- the error flag is cleared automatically and the state transitions to the Ready state.

- When the number of the error detection is more than the number of the auto-restoration,

- the state transitions to the Ready state by clearing the error flag.

#### <u>Any</u>

Any state as shown above.

Transfer Conditions:

- · If this IC detects UVLO, the state transitions to the No Supply state.

- If the HRSTB pin is "Low", the state transitions to the Reset state.

- BIST Check error

- Overcurrent / Reverse current Protection of DCDCs (REG1, REG2)

- Over-voltage of window voltage detection

- Under-voltage of window voltage detection - Regulator's ON and OFF timeout

- Internal Clock frequency Error

# Nisshinbo Micro Devices Inc.

<sup>&</sup>lt;sup>(1)</sup> The VINIO power input is required to access through the I<sup>2</sup>C-bus interface.

<sup>&</sup>lt;sup>(2)</sup> SM detects the errors as shown below. For further details of SM, refer to "Safety Mechanism". - BIST check error

No.EC-622-220627

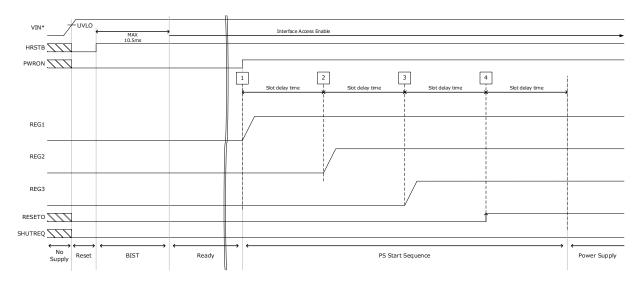

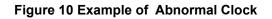

#### Power Supply (PS) Start Sequence

By a power supply start request in the Power Supply state, each regulator is turned on sequentially. [Power Supply Start Request]

PWRON: High-level input to the PWRON pin.

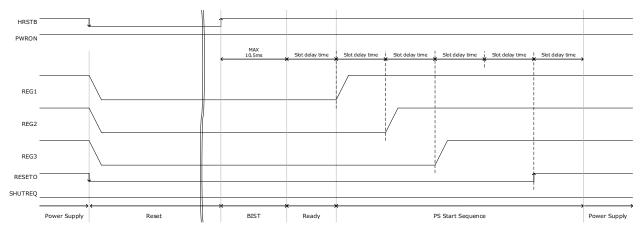

Figure 2 Example of PS Start Sequence

The turn-on sequence of regulators (hereinafter REGs) is programmable. Select the slot number for the ontiming of each REG in the range of 1 to 3. It is able to have a delay time after detection for the on-timing of each REG. The delay value is user-programmable from among 1.8ms, 3.6ms, 7.2ms or 14.4ms (Refer to *"Power Supply Start/Stop Slot Delay Time Setting Register"*).

The following conditions are provided for the example in Figure 2.

- REG1 : Start Slot Number = 1

- REG2 : Start Slot Number = 2

- REG3 : Start Slot Number = 3

- RESETO : Start Slot Number = 4

No.EC-622-220627

## [Always-on Regulator Power Supply Start Request]

After the completion of BIST, the always-on regulator is turned on to start.

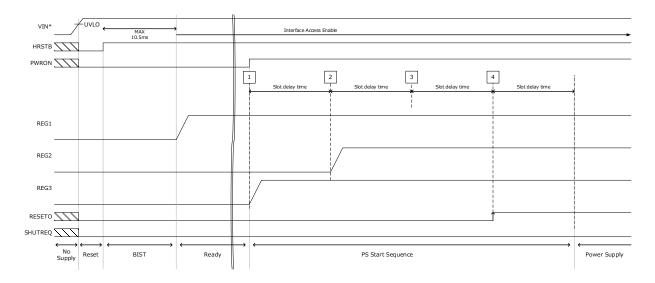

#### Figure 3 PS Example of Start Sequence with Always-on

Figure 3 is shown the turn-on timing of always-on regulator after the completion of the BIST. The following conditions are provided for the example in Figure 3.

- REG1 : Always-on

- REG2 : Start Slot Number = 2

- REG3 : Start Slot Number = 1

- RESETO : Start Slot Number = 4

No.EC-622-220627

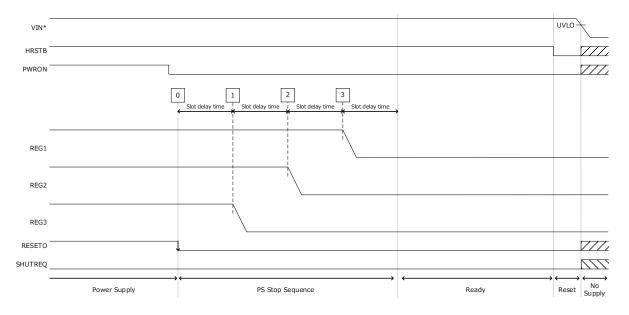

#### Power Supply (PS) Stop Sequence

By a power supply stop request in the Power Supply state, each regulator is turned off sequentially.

## [Power Supply Stop Request]

PWRON: Low-level input to the PWRON pin.

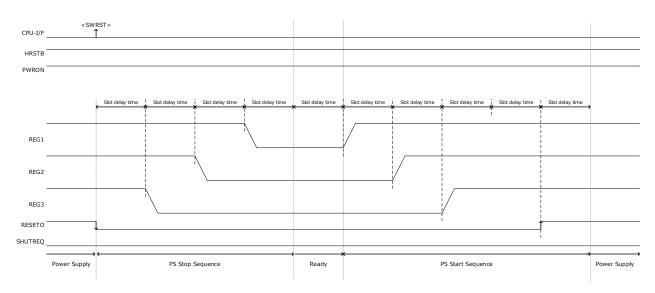

Figure 4 Example of PS Stop Sequence

The turn-off sequence of regulators is programmable. The off-timing of each REG can be delayed from the falling edge of PWRON and the delay value of each regulator is programmable. Select the number of slots for the off-timing of each regulator in the range of 1 to 4. The delay value of one slot is the same as PS Stop Sequence.

The following conditions are provided for the example in Figure 4.

- REG1: Stop Slot Number = 3

- REG2: Stop Slot Number = 2

- REG3: Stop Slot Number = 1

The RESETO pin becomes low-level at the timing of PWRON changed.

No.EC-622-220627

#### **Repower Sequence**

Once a repower request is detected in the Power Supply state, the state transitions to the PS Stop Sequence state and returns to the Power Supply state via the Ready and the PS Start Sequence states.

#### [Repower-on Request]

<SWREP>: CPU's writing to a dedicated register.

## Figure 5 Example of Repower-on Sequence

The following conditions are provided for the example in Figure 5.

- REG1 : Stop Slot Number = 3

- REG2 : Stop Slot Number = 2

- REG3 : Stop Slot Number = 1

- REG1 : Start Slot Number = 1

- REG2 : Start Slot Number = 2

- REG3 : Start Slot Number = 3

- RESETO : Start Slot Number = 5

The RESETO pin becomes low-level at the timing of PWRON changed.

No.EC-622-220627

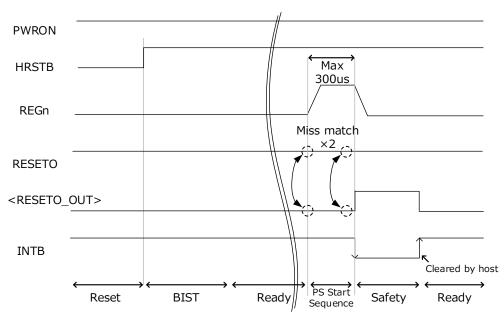

#### **Hardware Reset**

If a hardware reset request is detected in any state, the state transitions to the Reset state.

## [Hardware Reset Request]

HRSTB: Low-level input to the HRSTB pin.

## Figure 6 Example of Hardware Reset

The following conditions are provided for the example in Figure 6.

- REG1: Start Slot Number = 1

- REG2: Start Slot Number = 2

- REG3: Start Slot Number = 3

All REGs are turned off, the RESETO pin becomes low-level at the timing of HRSTB changed.

No.EC-622-220627

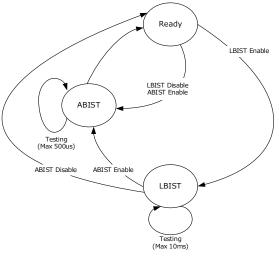

## **Built-In Self-Test (BIST)**

This IC includes Built-in Self-test (BIST) that runs under the following conditions.

- Entering Ready state from Reset state.

- Entering Ready state from any state when register has the BIST request.

Figure 7 BIST Flow

In the order of the tests, first comes logic (LBIST) and then analog (ABIST). When detecting an error, the BIST generates an interrupt and stores the detected block information in the register.

The target block of analog BIST is as follows.

- EXTDET

- REG3DET

- REG2DET

- REG1DET

- REG3 (LDO)

- REG2 (DCDC)

- REG1 (DCDC)

- IODET

- UVLO\_D

- UVLO\_A

- VINCMP

- TRIMMING CELL

No.EC-622-220627

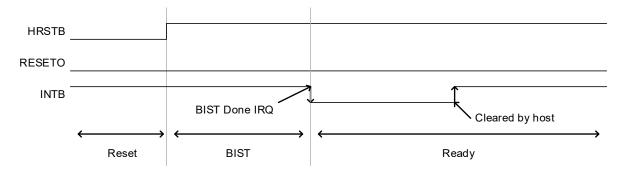

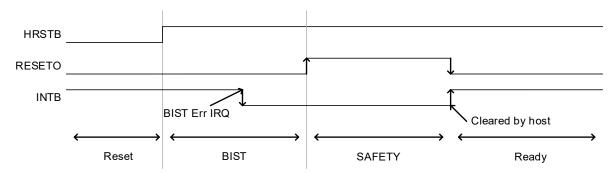

Figure 8 Example of BIST Done IRQ

An interrupt occurs at the completion of BIST. The interrupt can be masked by trimming.

Figure 9 Example of BIST Error IRQ

When detecting an error during the BIST, this device shifts to the Safety state at the completion of the BIST and maintains it until the interrupt factor is cleared.

No.EC-622-220627

## Safety Mechanism

This IC can detect the following errors.

- 1. Abnormal Clock Frequency and Clock Stop

- 2. REGn PS Start Sequence Timeout

- 3. REGn Soft-start Time Error

- 4. DCDC Overcurrent Protect

- 5. REGn Over/Under-Voltage

- 6. EXDET1 Over/Under Voltage

- 7. REGn Slot Violation

- 8. Abnormal RESETO Pin Release

- 9. VIN Monitor

When detecting an error, this IC performs the following functions.

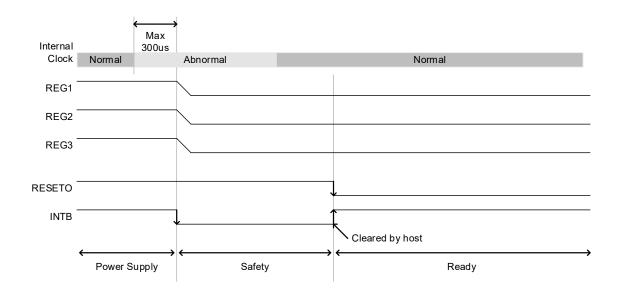

## 1. Abnormal Clock Frequency and Clock Stop

When detecting an abnormal oscillation, this IC outputs interrupt request and all REGs are turned off.

No.EC-622-220627

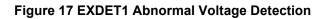

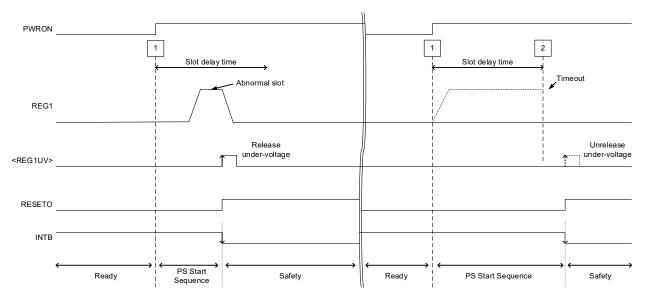

#### 2. REGn PS Start Sequence Timeout

A timeout error indicates that the output of REGn has not reached the target voltage within the slot delay time.

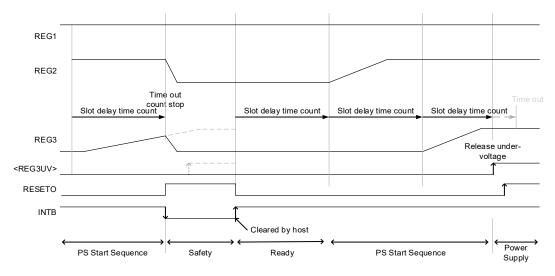

#### Figure 11 PS Start Timeout Judge Timing

The following conditions are provided for the examples in Figure 8, 9 and 10.

- REG1: Start Slot Number = Always-on

- REG2: Start Slot Number = 2

- REG3: Start Slot Number = 1

When detecting a PS Start timeout, this IC outputs interrupt request and all REGs are turned off.

Figure 12 PS Start Timeout Error

No.EC-622-220627

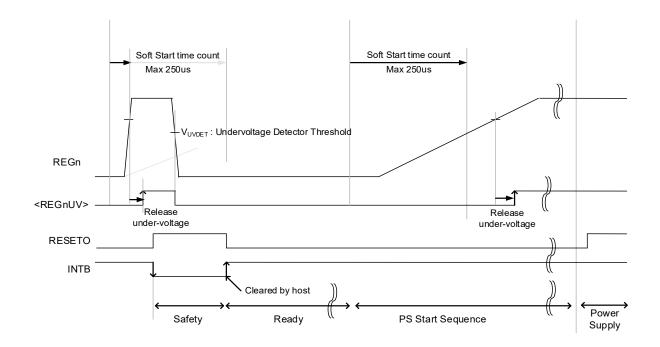

## 3. REGn Soft-start Time Error

The error of soft-start time indicates a short rising time of the REGn output. The count value of soft-start for one-slot is 250 µs (Max.).

Figure 13 Soft-start Time Error

When the REGn starts within 250  $\mu$ s (Max.) of the slot-start to release an under-voltage, this IC handles as the REGn soft-start error.

No.EC-622-220627

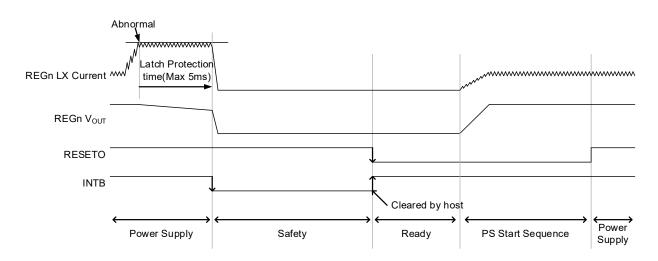

#### 4. DCDC Overcurrent Protect

The Step-down DCDC Converter (REG1, REG2) has an overcurrent latch protection circuit to detect continuous overcurrent. When detecting an overcurrent, this IC outputs an interrupt request and all REGs except Always-on REG are turned off.

Figure 14 DCDC Overcurrent Error

No.EC-622-220627

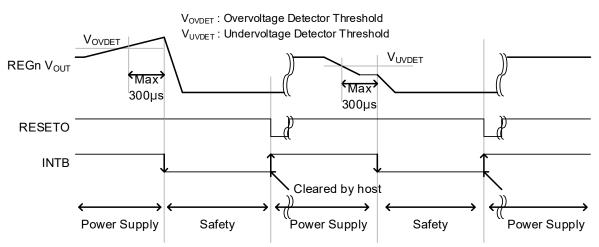

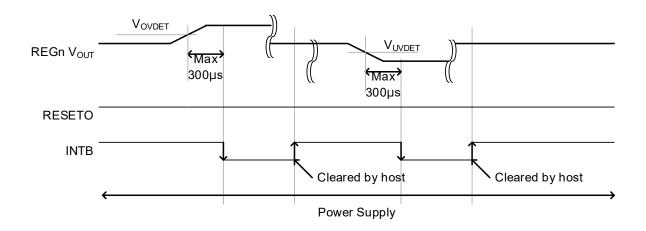

#### 5. REGn Over/Under-Voltage

The window voltage detector monitors REGn voltage. When detecting over/under-voltage, this IC outputs interrupt request and REGn is turned off.

In addition, it is over-voltage also when it is ON of REGn (except Always-on REG) in the READY State. The turn-off function can disable. In addition, this IC can turn off other REG at the same timing (Refer to "Auto-off setting Register"). If REGn remains on, the RESETO pin also remain on.

Figure 15 REGn Abnormal Voltage Detection with REG OFF

Figure 16 REGn Abnormal Voltage Detection with REG ON

No.EC-622-220627

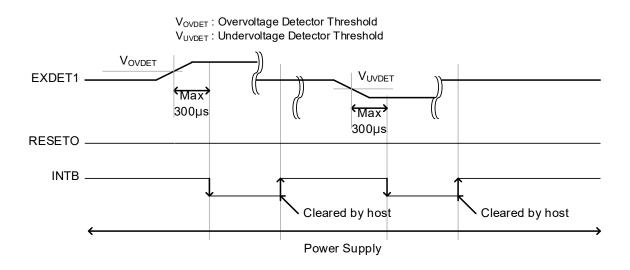

## 6. EXDET1 Over/Under Voltage

When the window voltage detector monitoring the EXDET1 pin voltage detects an over/under-voltage, this IC outputs the interrupt request only.

No.EC-622-220627

## 7. REGn Slot Violation

When detecting the slot violation for the REGn start, this IC generates an interrupt to stop the REGn. The detecting conditions for the slot violation are as follows:

- Don't start REGn in the specified slot.

- Starts REGn in the another except the specified slot.

Figure 18 Example of Start Slot Violation

The following condition is provided for the example in Figure 18.

• REG1: Start Slot Number = 2

In this example, when the REG1 starts up before the specified slot (Slot2), this IC handles as an over-voltage detection for REG1. When the REG1 does not start up in the specified slot, this IC handles as timeout for REG1.

This IC works as for the above cases even if an error occurs in the slot period. For example, if the slot period becomes short, this IC handles as a timeout because the REGn does not start up.

No.EC-622-220627

#### 8. Abnormal RESETO Pin Release

The IC monitors the status of the RESETO pin. When detecting an abnormal reset release, this IC outputs an interrupt request and turns all REGn off.

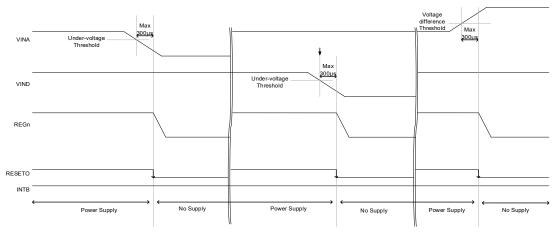

#### 9. VIN Monitor

This IC monitors the voltages for VINA and VIND pins all the time. When detecting a low-voltage or an abnormal voltage-difference between the pins, this IC is shut down.

**Figure 20 VIN Monitor**

# Nisshinbo Micro Devices Inc.

No.EC-622-220627

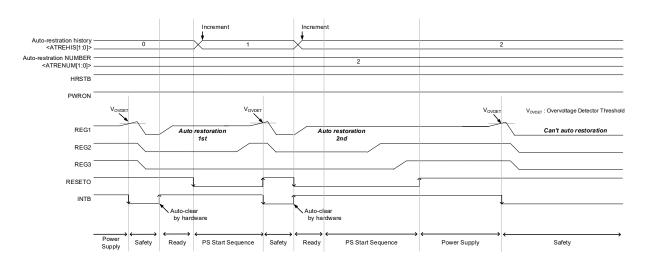

#### **Auto-restoration Sequence**

Auto-restoration Sequence

The auto-restoration functions at the error <sup>(1)</sup> detection. The auto-restoration time is able to select from 0 to 3 (Refer to "System Control Register"). If the error detection times is not more than it, the error flag is cleared automatically and the state transitions to the Power Supply state via the Ready and the PS Start Sequence state.

#### [Auto-restoration Condition]

The error detection times is not more than the auto-restoration times (ATRENUM bits).

#### Figure 21 Auto-restoration Sequence

The following conditions are provided for the example in Figure 22.

- REG1: Always-on

- REG2: Slot On

- REG3: Slot On

$^{\left( 1\right) }$  The errors are shown below.

- Overcurrent / Reverse current Protection of DCDCs (REG1, REG2)

- Over-voltage of window voltage detection of REGn

- Under-voltage of window voltage detection of REGn

- Timeout of power supply sequence

- Short rise time of REGn Soft-start

- Detection of abnormal temperature

# Nisshinbo Micro Devices Inc.

No.EC-622-220627

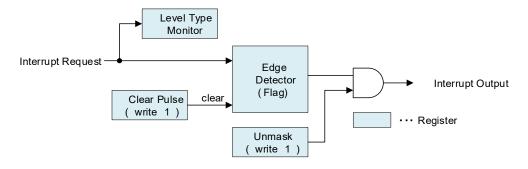

## Interrupt Controller (INTC)

This IC has an open-drain output INTB (Interrupt) pin. This pin is used to indicate an interrupt request state. "Hiz" is non-request. "Low" is request.

Interrupt Request factors are as follows.

- · Detection and release of abnormal temperature

- Over-voltage output of REGn

- Under-voltage output of REGn

- Overcurrent and reverse current of DCDCs (REG1, REG2)

- Timeout of power supply sequence

- Short rise time of REGn soft-start.

- EXDET1 pin over-voltage detection

- EXDET1 pin under-voltage detection

- BIST error detection

- I<sup>2</sup>C error

- · BIST done

The interrupt request is set in the INTREQ register by this IC and cleared by host writing "1". The flag can be masked with the unmask register.

Figure 22 INTC Block Diagram

Note: When using the interrupt controller, the pull-up resistance of 10 k $\Omega$  to 100 k $\Omega$  for INTB pin is recommended. When not using it, the INTB pin must be left floating or connected to GND.

No.EC-622-220627

## Shut-down Request (SHUTREQ)

The SHUTREQ pin is used to protect against an error that cannot turn off REG1,2,3 of this IC. It is assumed that the power supply from primary DCDC will be stopped by receiving the output of the SHUTREQ pin.

The SHUTREQ pin issues a request to shut this IC down when the following factor occurs.

- Over-voltage output of REGn

- Under-voltage output of REGn

- Overcurrent and reverse current of DCDCs (REG1, REG2)

- Short rise time of REGn soft-start

- REGn PS Start sequence timeout

These factors can be masked in the register. The occurrence of a masked factor causes a transition to the Safety state, but the SHUTREQ pin keeps Low output.

Figure 23 Shutdown Request (Ex:REG1 Over-voltage)

# Nisshinbo Micro Devices Inc.

No.EC-622-220627

# **VOLTAGE DETECTOR**

## **Electrical Characteristics**

$V_{SYS}$  =  $V_{SYS_TYP}$ , unless otherwise specified.

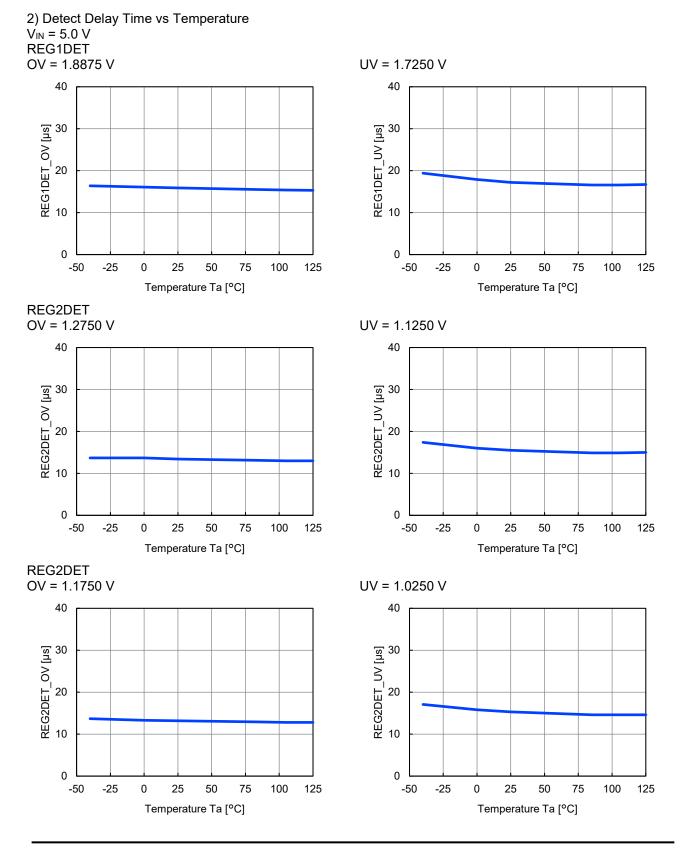

| REG1DET, | <b>REG2DET Electrical Ch</b>                     |                           | (–40°C ≤ Ta ≤ 125°C) |         |                            |         |      |

|----------|--------------------------------------------------|---------------------------|----------------------|---------|----------------------------|---------|------|

| Symbol   | Parameter                                        | C                         | ondition             | Min.    | Тур.                       | Max.    | Unit |

| Vovrange | Overvoltage (OV)<br>Detector Threshold<br>Range  |                           | -                    | 0.6     |                            | 3.7     | V    |

| Vuvrange | Undervoltage (UV)<br>Detector Threshold<br>Range |                           |                      | 0.6     |                            | 3.7     | V    |

|          | Overvoltage (OV)<br>Detector Threshold           | V <sub>OVDET</sub> ≥ 1.0V | Ta = 25°C            | × 0.99  | $V_{\text{OVDET}}{}^{(1)}$ | × 1.01  | V    |

|          |                                                  |                           | –40°C ≤ Ta ≤ 125°C   | × 0.985 | Vovdet <sup>(1)</sup>      | × 1.011 | V    |

| Vovdet   |                                                  | V <sub>OVDET</sub> < 1.0V | Ta = 25°C            | × 0.987 | Vovdet <sup>(1)</sup>      | × 1.013 | V    |

|          |                                                  |                           | –40°C ≤ Ta ≤ 125°C   | × 0.976 | Vovdet <sup>(1)</sup>      | × 1.016 | V    |

|          |                                                  |                           | Ta = 25°C            | × 0.99  | VUVDET <sup>(1)</sup>      | × 1.01  | V    |

| N/       | Undervoltage (UV)                                | V <sub>UVDET</sub> ≥ 1.0V | –40°C ≤ Ta ≤ 125°C   | × 0.985 | VUVDET <sup>(1)</sup>      | × 1.011 | V    |

| VUVDET   | Detector Threshold                               | V < 1.0V                  | Ta = 25°C            | × 0.987 | VUVDET <sup>(1)</sup>      | × 1.013 | V    |

|          |                                                  | VUVDET < 1.0V             | –40°C ≤ Ta ≤ 125°C   | × 0.976 | VUVDET <sup>(1)</sup>      | × 1.016 | V    |

| tovdelay | OV Detect Delay Time                             |                           |                      |         |                            | 300     | μs   |

| tuvdelay | UV Detect Delay Time                             |                           |                      |         |                            | 300     | μs   |

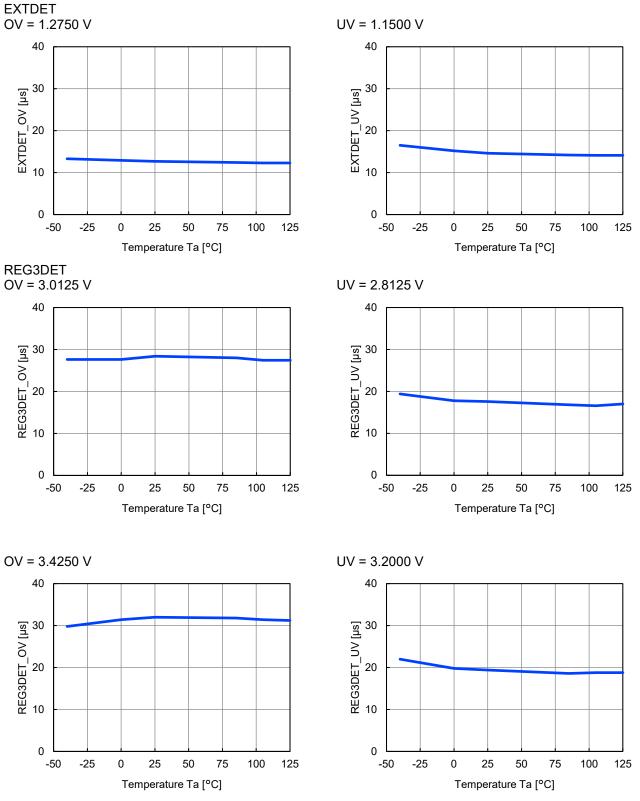

## **REG3DET Electrical Characteristics**

(–40°C ≤ Ta ≤ 125°C)

|          |                                               | $(-40 \ C = 10 = 125 \ C)$ |         |                            |         |      |

|----------|-----------------------------------------------|----------------------------|---------|----------------------------|---------|------|

| Symbol   | Parameter                                     | Condition                  | Min.    | Тур.                       | Max.    | Unit |

| VOVRANGE | Overvoltage (OV) Detector<br>Threshold Range  | -                          | 2.0     |                            | 4.0     | V    |

| VUVRANGE | Undervoltage (UV) Detector<br>Threshold Range |                            | 2.0     |                            | 4.0     | V    |

| N/       | Overvoltage (OV) Detector<br>Threshold        | Ta = 25°C                  | × 0.99  | $V_{\text{OVDET}}{}^{(1)}$ | × 1.01  | V    |

| Vovdet   |                                               | –40°C ≤ Ta ≤ 125°C         | × 0.985 | Vovdet <sup>(1)</sup>      | × 1.011 | V    |

| VUVDET   | Undervoltage (UV) Detector                    | Ta = 25°C                  | × 0.99  | $V_{\text{UVDET}}^{(1)}$   | × 1.01  | V    |

| VUVDEI   | Threshold                                     | –40°C ≤ Ta ≤ 125°C         | × 0.985 | $V_{\text{UVDET}}{}^{(1)}$ | × 1.011 | V    |

| tovdelay | OV Detect Delay Time                          |                            |         |                            | 300     | μs   |

| tuvdelay | UV Detect Delay Time                          |                            |         |                            | 300     | μs   |

$<sup>^{(1)}</sup>V_{\text{OVDET}}$  and  $V_{\text{UVDET}}$  are selectable by trimming.

No.EC-622-220627

| EXTDET E | lectrical Characteristics                        |                                                      | (–40°C ≤ Ta ≤ 125°C)      |           |                          |                 |        |   |

|----------|--------------------------------------------------|------------------------------------------------------|---------------------------|-----------|--------------------------|-----------------|--------|---|

| Symbol   | Parameter                                        | C                                                    | Condition                 | Min.      | Тур.                     | Max.            | Unit   |   |

| Vovrange | Overvoltage (OV)<br>Detector Threshold<br>Range  |                                                      | -                         | 0.6       |                          | 3.7             | V      |   |

| Vuvrange | Undervoltage (UV)<br>Detector Threshold<br>Range |                                                      |                           | 0.6       |                          | 3.7             | V      |   |

|          | Overvoltage (OV)<br>Detector Threshold           | N/ S                                                 | V <sub>OVDET</sub> ≥ 1.0V | Ta = 25°C | × 0.99                   | $V_{OVDET}$ (1) | × 1.01 | V |

| Max      |                                                  | VOVDET 2 1.0V                                        | –40°C ≤ Ta ≤ 125°C        | × 0.985   | Vovdet <sup>(1)</sup>    | × 1.011         | V      |   |

| Vovdet   |                                                  | V <sub>OVDET</sub> < 1.0V                            | Ta = 25°C                 | × 0.987   | Vovdet <sup>(1)</sup>    | × 1.013         | V      |   |

|          |                                                  |                                                      | –40°C ≤ Ta ≤ 125°C        | × 0.976   | Vovdet <sup>(1)</sup>    | × 1.016         | V      |   |

|          |                                                  | V <sub>UVDET</sub> ≥ 1.0V                            | Ta = 25°C                 | × 0.99    | VUVDET <sup>(1)</sup>    | × 1.01          | V      |   |

| N/       | Undervoltage (UV)                                |                                                      | –40°C ≤ Ta ≤ 125°C        | × 0.985   | $V_{\text{UVDET}}^{(1)}$ | × 1.011         | V      |   |

| VUVDET   | Detector Threshold                               | V < 1.0V                                             | Ta = 25°C                 | × 0.987   | VUVDET <sup>(1)</sup>    | × 1.013         | V      |   |

|          |                                                  | V <sub>UVDET</sub> < 1.0V                            | –40°C ≤ Ta ≤ 125°C        | × 0.976   | VUVDET <sup>(1)</sup>    | × 1.016         | V      |   |

| RSENSE   | SENSE Resistance                                 | V <sub>OVDET</sub> = 1.2V, V <sub>UVDET</sub> = 1.0V |                           | 0.5       | 1.2                      | 2.5             | MΩ     |   |

| tovdelay | OV Detect Delay Time                             |                                                      |                           |           |                          | 300             | μs     |   |

| tuvdelay | UV Detect Delay Time                             |                                                      |                           |           |                          | 300             | μs     |   |

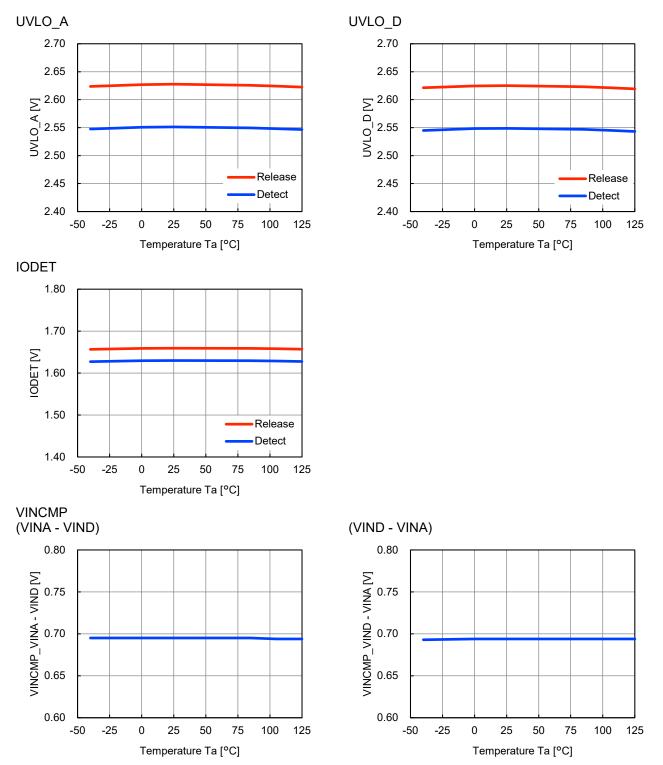

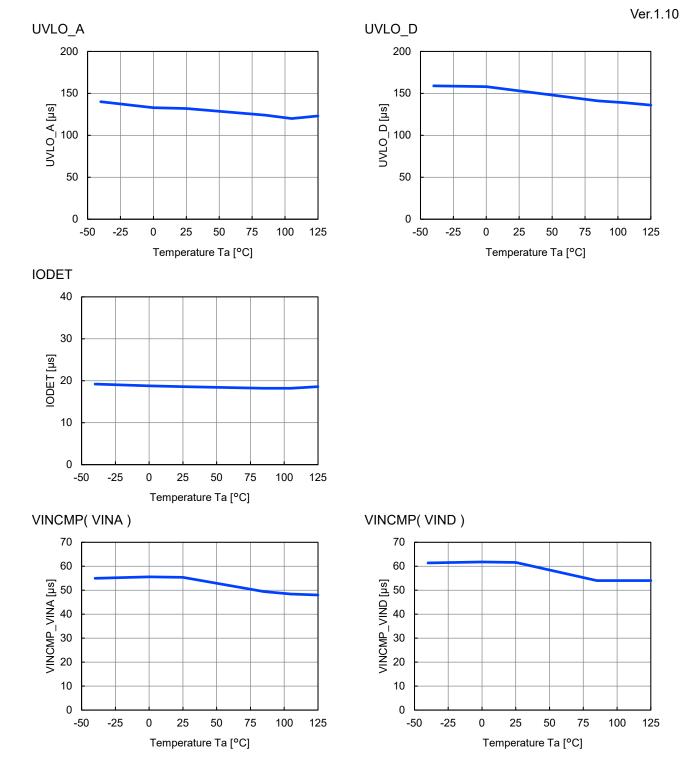

| UVLO Elec          | JVLO Electrical Characteristics $(-40^{\circ}C \le 7)$ |                       |      |      |      | 25°C) |

|--------------------|--------------------------------------------------------|-----------------------|------|------|------|-------|

| Symbol             | Parameter                                              | Condition             | Min. | Тур. | Max. | Unit  |

| Vdet               | Detect Voltage                                         |                       | 2.5  | 2.55 | 2.6  | V     |

| VREL               | Release Voltage                                        |                       | 2.55 |      | 2.7  | V     |

| t <sub>DELAY</sub> | Detect Delay Time                                      | C <sub>IN</sub> = 1µF |      |      | 300  | μs    |

|                               | VINCMP Electrical Characteristics |                       |      |      | ≤ Ta ≤ 1: | 25°C) |

|-------------------------------|-----------------------------------|-----------------------|------|------|-----------|-------|

| Symbol                        | Parameter                         | Condition             | Min. | Тур. | Max.      | Unit  |

| $V_{\text{DET}\_\text{VIND}}$ | VIND-VINA Detect Voltage          |                       | 0.3  |      | 1.0       | V     |

| VDET_VINA                     | VINA-VIND Detect Voltage          |                       | 0.3  |      | 1.0       | V     |

| <b>t</b> DELAY                | Detect Delay Time                 | C <sub>IN</sub> = 1µF |      |      | 300       | μs    |

| IODET Ele        | IODET Electrical Characteristics |           |      |      | ≤ Ta ≤ 1 | 25°C) |

|------------------|----------------------------------|-----------|------|------|----------|-------|

| Symbol           | Parameter                        | Condition | Min. | Тур. | Max.     | Unit  |

| Vdet             | Detect Voltage                   |           | 1.6  | 1.63 | 1.66     | V     |

| V <sub>REL</sub> | Release Voltage                  |           | 1.62 |      | 1.70     | V     |

| <b>t</b> DELAY   | Detect Delay Time                |           |      |      | 300      | μs    |

$^{(1)}V_{\text{OVDET}}$  and  $V_{\text{UVDET}}$  are selectable by trimming.

No.EC-622-220627

## REGULATOR

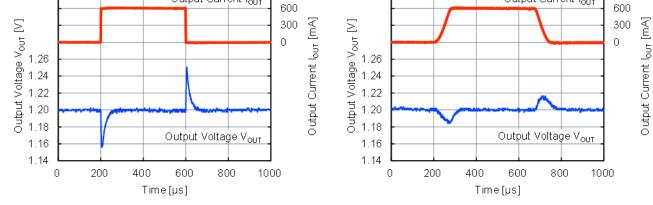

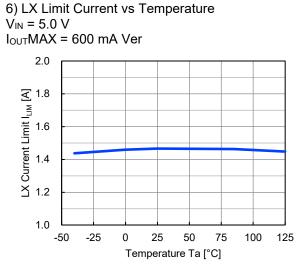

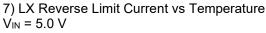

## DCDC (REG1, REG2) Electrical Characteristics

$V_{SYS}$  =  $V_{SYS_TYP}$ , unless otherwise specified.

| REG1, REG           | <b>REG1, REG2 Electrical Characteristics</b> (-40°C ≤ Ta ≤ 125°C |                                                  |        |                                 |        | 25°C) |

|---------------------|------------------------------------------------------------------|--------------------------------------------------|--------|---------------------------------|--------|-------|

| Symbol              | Parameter Condition                                              |                                                  | Min.   | Тур.                            | Max.   | Unit  |

| Vout                | Output Maltana                                                   | Ta = 25°C                                        | × 0.99 | Vset <sup>(1)</sup>             | × 1.01 | v     |

| VOUT                | Output Voltage                                                   | −40°C ≤ Ta ≤ 125°C                               | × 0.97 | VSET <sup>(1)</sup>             | × 1.03 | v     |

| LXLIM1              | LX Current Limit1                                                | I <sub>OUTMAX</sub> = 600 mA Ver <sup>(2)</sup>  | 900    | 1400                            | 1900   | mA    |

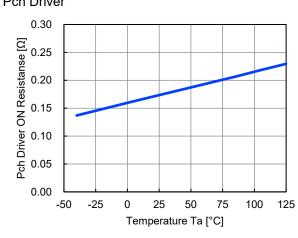

| I <sub>LXLIM2</sub> | LX Current Limit2                                                | I <sub>OUTMAX</sub> = 1000 mA Ver <sup>(2)</sup> | 1300   | 1900                            | 2600   | mA    |

| <b>t</b> PROT       | Protection Delay Time                                            |                                                  | 0.5    | 1.5                             | 5      | ms    |

| tprot_rev           | Protection Delay Time<br>(Reverse Current)                       |                                                  | 0.5    | 1.5                             | 5      | ms    |

| REVLIM              | Reverse Current Limit                                            |                                                  | -2700  | -1400                           | -600   | mA    |

| fosc                | LX Oscillator<br>Frequency                                       |                                                  | 2.0    | 2.3                             | 2.5    | MHz   |

| <b>t</b> start      | Soft-start Time                                                  | Time from Enable to 90% of $V_{OUT}$             | × 0.5  | t <sub>SET</sub> <sup>(3)</sup> | × 2.0  | ms    |

| RLOW                | On Resistance of Low<br>Output                                   | V <sub>SYS</sub> = 3.0V, VOUT1, 2 = 0.1V         |        | 5                               | 18     | Ω     |

Test circuit is operated with "Open Loop Control" (GND = 0 V), unless otherwise specified.

<sup>&</sup>lt;sup>(1)</sup> V<sub>SET</sub> is selectable from 1.0 V to 3.3 V by trimming. V<sub>SET</sub> must be less than or equal to "V<sub>SYS</sub> (Min.) -1.0V".

<sup>(2)</sup> I<sub>OUTMAX</sub> is selectable from 600mA / 1000mA by trimming.

$<sup>^{(3)}</sup>$  t<sub>SET</sub> is selectable from four set times (0.5 / 1.0 / 2.0 / 4.0 ms) by trimming.

No.EC-622-220627

## **OSC Electrical Characteristics**

$V_{SYS}$  =  $V_{SYS_TYP}$ , unless otherwise specified.

| OSC23M1, OSC23M2 Electrical Characteristics |                                               |                   |       | (–40° | C ≤ Ta ≤ | 125°C) |

|---------------------------------------------|-----------------------------------------------|-------------------|-------|-------|----------|--------|

| Symbol                                      | Parameter                                     | Condition         | Min.  | Тур.  | Max.     | Unit   |

| fosc                                        | Oscillator Frequency                          |                   | 2.0   | 2.3   | 2.5      | MHz    |

| <b>f</b> DIFF                               | Frequency Difference                          | OSC23M1 - OSC23M2 | -146  |       | 149      | kHz    |

| fdetl1                                      | OSC23M1<br>Low Frequency<br>Detect Threshold  | OSC23M2 = 2MHz    | 1.854 |       |          | MHz    |

| fdeth1                                      | OSC23M1<br>High Frequency<br>Detect Threshold | OSC23M2 = 2.5MHz  |       |       | 2.702    | MHz    |

| fdetl2                                      | OSC23M2<br>Low Frequency<br>Detect Threshold  | OSC23M1 = 2MHz    | 1.850 |       |          | MHz    |

| f <sub>DETH2</sub>                          | OSC23M2<br>High Frequency<br>Detect Threshold | OSC23M1 = 2.5MHz  |       |       | 2.698    | MHz    |

| t <sub>DELAY</sub>                          | Detect Delay Time                             |                   |       |       | 300      | μs     |

. .

No.EC-622-220627

## LDO (REG3) Electrical Characteristics

V<sub>SYS</sub> = V<sub>SYS\_TYP</sub>, I<sub>OUT</sub> = 1 mA, unless otherwise specified.

| REG3 Electric                  | cal Characteristics            |                                                   |         | (-40°                           | °C ≤ Ta ≤ ′ | 125°C) |

|--------------------------------|--------------------------------|---------------------------------------------------|---------|---------------------------------|-------------|--------|

| Symbol                         | Parameter                      | Condition                                         | Min.    | Тур.                            | Max.        | Unit   |

|                                |                                | Ta = 25°C                                         | × 0.99  | V <sub>SET</sub> <sup>(1)</sup> | × 1.01      | V      |

| Vout                           | Output Voltage                 | -40°C ≤ Ta ≤ 125°C.                               | × 0.985 | $V_{SET}^{(1)}$                 | × 1.015     | V      |

| ΔVουτ/ΔΙουτ                    | Load Regulation                | 1 mA ≤ I <sub>OUT</sub> ≤ 200 mA                  | -10     | 5                               | 10          | mV     |

| VDIF                           | Dropout Voltage                | louт = 200 mA                                     |         |                                 | 200         | mV     |

| $\Delta V_{OUT}/\Delta V_{IN}$ | Line Regulation                | $V_{SET}^{(1)}$ +0.5 V ≤ $V_{SYS}$ ≤ 5.5 V,       |         | 0.02                            | 0.10        | %/V    |

| ILIM1                          | Limit Current1                 | IOUTMAX = 100 mA Ver <sup>(2)</sup>               | 100     | 140                             | 180         | mA     |

| I <sub>LIM2</sub>              | Limit Current2                 | IOUTMAX = 200 mA Ver <sup>(2)</sup>               | 200     | 280                             | 360         | mA     |

| lsc                            | Short Current Limit            | V <sub>OUT</sub> = 0 V                            | 40      | 75                              | 100         | mA     |

| <b>t</b> start                 | Soft-start Time                | Time from Enable to 90% of Vout                   | × 0.5   | tset <sup>(3)</sup>             | × 2.0       | ms     |

| RLOW                           | On Resistance of<br>Low Output | V <sub>SYS</sub> = 3.0V, V <sub>OUT3</sub> = 0.1V |         | 15                              | 30          | Ω      |

$<sup>^{(1)}</sup> V_{\text{SET}} \text{ is selectable from } 2.5 \text{ V to } 3.5 \text{ V by trimming.} \\ V_{\text{SET}} \text{ must be less than or equal to "Vsys(Min.)} - 0.5 \text{ V"}.$   $^{(2)} \text{ loutMAX is selectable from } 100\text{mA} \text{ / } 200\text{mA by trimming.}$

<sup>&</sup>lt;sup>(3)</sup> t<sub>SET</sub> is selectable from four set times (0.5 / 1.0 / 2.0 / 4.0 ms) by trimming.

No.EC-622-220627

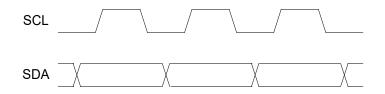

# I<sup>2</sup>C-BUS INTERFACE

This IC supports the I<sup>2</sup>C-bus system with two-wires for connecting the CPU. Connection and Transfer system of the I<sup>2</sup>C-bus are described in the following sections.

## I<sup>2</sup>C-Bus Operation

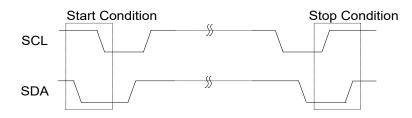

Within the procedure of I<sup>2</sup>C-bus, unique situations arise which are defined as start and stop conditions.

Figure 24 I<sup>2</sup>C-Bus Data Transmission

A "High" to "Low" transition on SDA line while SCL is "High" indicates a start condition. A "Low" to "High" transition on SDA line while SCL is "High" defines a stop condition. Start and stop conditions are always generated by master (Refer to the figure below). The bus is considered to be busy after start condition. The bus is considered to be free again a certain time after the stop condition.

Figure 25 I<sup>2</sup>C-Bus Start / Stop Condition

No.EC-622-220627

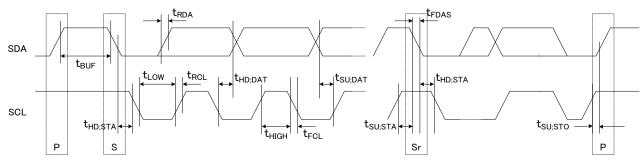

## AC Characteristics of I<sup>2</sup>C-Bus

$V_{INIO}$  = 1.8 V,  $C_B^{(1)}$  = 550 pF (Max.), unless otherwise specified.

| Fast-mode Plus (Fm+) |                                             |           |      |      | C ≤ Ta ≤ ′ | 125°C) |

|----------------------|---------------------------------------------|-----------|------|------|------------|--------|

| Symbol               | Parameter                                   | Condition | Min. | Тур. | Max.       | Unit   |

| <b>f</b> scL         | SCL Clock Frequency                         | -         |      |      | 1000       | kHz    |

| t <sub>BUF</sub>     | Bus Free Time Between a Precedent and Start | -         | 0.5  |      | -          | μs     |

| t∟ow                 | SCL Clock Time, "Low"                       | -         | 0.5  |      | -          | μs     |

| tнigн                | SCL Clock Time, "High"                      | -         | 0.26 |      | -          | μs     |

| <b>t</b> su;sta      | Start Condition Setup Time                  | -         | 0.26 |      | -          | μs     |

| thd;sta              | Start Condition Hold Time                   | -         | 0.26 |      | -          | μs     |

| <b>t</b> su;sто      | Stop Condition Setup Time                   | -         | 0.26 |      | -          | μs     |

| thd;dat              | Data Hold Time                              | -         | 0    |      |            | μs     |

| t <sub>su;dat</sub>  | Data Setup Time                             | -         | 50   |      | -          | ns     |

| t <sub>R</sub>       | Rising Time of SCL and SDA (Input)          | -         |      |      | 120        | ns     |

| t⊧                   | Falling Time of SCL and SDA (Input)         | -         |      |      | 120        | ns     |

| t <sub>SP</sub>      | Suppressing Pulse Width                     | -         | 0    |      | 50         | ns     |

Note: All the above-mentioned values are corresponding to VIH min and VIL max level.

Figure 26 I<sup>2</sup>C-Bus Interface Timing Chart

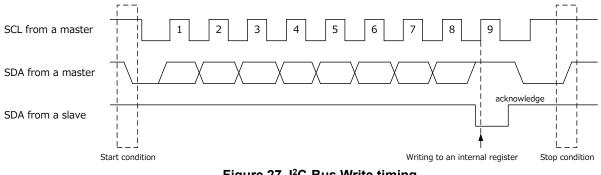

# I<sup>2</sup>C-Bus Internal Register Write-in Timing

Figure 27 I<sup>2</sup>C-Bus Write timing

$^{(1)}$  C<sub>B</sub>: Capacitive load for each bus line

# Nisshinbo Micro Devices Inc.

No.EC-622-220627

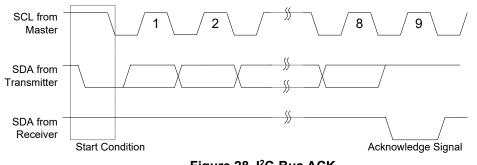

#### I<sup>2</sup>C-Bus Data Transmission and Its Acknowledge

After start condition, data is transmitted by 1-byte (8-bit). The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an acknowledge bit. Data transmission with acknowledge is obligatory. The acknowledge-related clock pulse is generated by the master. The transmitter releases SDA line during the acknowledge clock pulse. The receiver must pull down SDA line during the acknowledge clock pulse. The receiver must pull down SDA line during the acknowledge clock pulse. If a master-receiver is involved in a transfer, it must signal the end of the data to the slave-transmitter by not generating acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line to allow the master to generate a stop condition.

#### Figure 28 I<sup>2</sup>C-Bus ACK

#### I<sup>2</sup>C-Bus Slave Address

After start condition, a slave address is sent. The address is 7-bit long followed by an 8-bit which is data direction bit (Read/Write). The slave address of this IC is selectable by trimming and pin.

|               | A7 | A6 | A5 | A4 | A3 <sup>(1)</sup> | A2 <sup>(2)</sup> | A1 <sup>(3)</sup> |

|---------------|----|----|----|----|-------------------|-------------------|-------------------|

| Slave Address | 0  | 1  | 1  | 0  | Х                 | Х                 | Х                 |

| Figure 29 | I <sup>2</sup> C-Bus Sla | ve Address |

|-----------|--------------------------|------------|

|-----------|--------------------------|------------|

<sup>(2)</sup> A [2] of the slave address are selectable by SLV2 pin. The state of SLV2 pin is stored when the reset is released.

<sup>(3)</sup> A [1] of the slave address are selectable by SLV1 pin. The state of SLV1 pin is stored when the reset is released.

<sup>&</sup>lt;sup>(1)</sup> A [3] of the slave address is selectable by trimming.

No.EC-622-220627

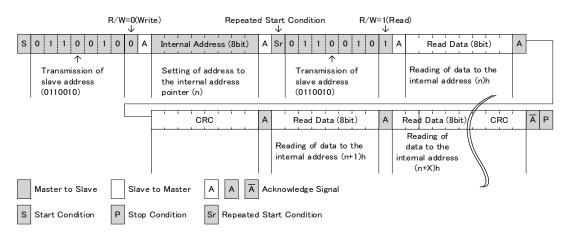

#### I<sup>2</sup>C-Bus Data Transmission Read Format

In order to read the internal register data:

- Specify an internal address pointer (8-bit).

- Generate the repeated start condition to change the data transmission direction to read.

With a start of read mode, automatic increment in address pointers will be made. Read mode is repeated until stop condition is initiated.

The format for read processing after the start condition consists as shown in the following figure.

1st byte: Slave address + Write instruction

2<sup>nd</sup> byte: Address for the internal register from which the data is to read.

3rd byte: Slave address + Read instruction

4<sup>th</sup> byte: Data read out from the address specified in the second byte.

5th byte: CRC data

The CRC data is an 8-bit data to indicate the result of the CRC error detection. The CRC data to the 16-bit data (In continuous reading, an 8-bit data immediately before the second and subsequent byte) immediately after restarting is given by the following polynomial.

$C(x) = X^8 + X^2 + X^1 + 1$

After the completion of the data transfer in the 5th byte, the master issues a non-acknowledgement signal and a stop condition continuously. After reading out, no enter of the non-acknowledgement and the stop condition, it is possible to read the data continuously. Then, the target address is incremented.

An example of the continuous read format is as follows:

Figure 30 I<sup>2</sup>C-Bus Read Format

No.EC-622-220627

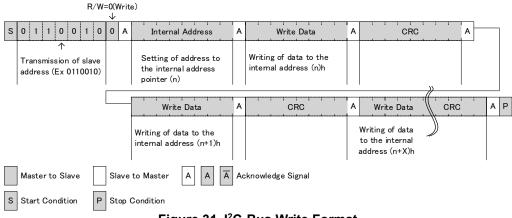

#### I<sup>2</sup>C-Bus Data Transmission Write Format

The transmission format for the slave address allocated to each IC is defined in the I<sup>2</sup>C-bus standard, but transmission method of address information of each IC is not defined. This IC transmits command data. For the data transmission, please transmit MSB first from master and following data in sequence.

The format for write processing after the start condition consists as shown in the following figure. 1<sup>st</sup> byte: Slave address + Write instruction 2<sup>nd</sup> byte: Address for internal register to which the data to write. 3<sup>rd</sup> byte: Data to write in the second byte. 4<sup>th</sup> byte: CRC data.

The CRC data is an 8-bit data to indicate the result of the CRC error detection. The CRC data to the 24-bit data (In continuous writing, an 8-bit data immediately before the second and subsequent byte) immediately after starting is given by the following polynomial.

$C(x) = X^8 + X^2 + X^1 + 1$

After writing the data, the stop condition is required. If transferring the data, which must be written into the register at the next address, and the CRC data by bypassing the stop condition, it is possible to write the data continuously. This IC determines whether a receive error is detected or not when the LSB of the CRC data is received. The interrupt occurs at detecting error (max. 50µs), but no transition to the Safety state occurs. Then, the target address is incremented. An example of the continuous write format is as follows:

Figure 31 I<sup>2</sup>C-Bus Write Format

No.EC-622-220627

### TRIMMING

The RN5T5611 functions and initial settings can be laser-trimmed as user required at shipping. Some functions are changeable by a programming via the  $l^2$ C-bus after startup.

| Item     | Descr                                | iption       | Register <sup>(1)</sup> | Set Values                                            |

|----------|--------------------------------------|--------------|-------------------------|-------------------------------------------------------|

|          | A3 Bit in I <sup>2</sup> C Slav      | ve Address   | -                       | 0: 0, 1: 1                                            |

| System   | Mask of BIST Completion<br>Interrupt |              | 26h[7]                  | 0: Mask, 1: UnMask                                    |

|          | Auto-restoration                     | times        | -                       | 0: 0, 1: 1, 2: 2, 3: 3                                |

|          | Slot Width                           |              | -                       | 0: 1.8ms, 1: 3.6ms, 2: 7.2ms, 3: 14.4ms               |

|          |                                      | REG1         | -                       | 0: Always ON, 1: Slot_1, 2: Slot_2, 3: Slot_3         |

|          | Power-on Slot                        | REG2         | -                       | 1: Slot_1, 2: Slot_2, 3: Slot_3                       |

| Seguence |                                      | REG3         | -                       | 1: Slot_1, 2: Slot_2, 3: Slot_3                       |

| Sequence |                                      | REG1         | -                       | 0: Slot_0, 1: Slot_1, 2: Slot_2, 3: Slot_3            |

|          | Power-off Slot                       | REG2         | -                       | 0: Slot_0, 1: Slot_1, 2: Slot_2, 3: Slot_3            |

|          |                                      | REG3         | -                       | 0: Slot_0, 1: Slot_1, 2: Slot_2, 3: Slot_3            |

|          | RESETO Output Slot                   |              | -                       | 1: Slot_1, 2: Slot_2, 3: Slot_3, 4: Slot_4, 5: Slot_5 |

|          |                                      | REG1         | -                       | $1.00V \le Source \le 3.30V$ (in 50mV step)           |

|          | Output Voltage                       | REG2         | -                       | $1.00V \le Source \le 3.30V$ (in 50mV step)           |

|          |                                      | REG3         | -                       | $2.50V \le Source \le 3.50V$ (in 50mV step)           |

|          |                                      | REG1         | -                       | 0: 0.5ms, 1: 1.0ms, 2: 2.0ms, 3: 4.0ms                |

| REGn     | Soft-start Time                      | REG2         | -                       | 0: 0.5ms, 1: 1.0ms, 2: 2.0ms, 3: 4.0ms                |

|          |                                      | REG3         | -                       | 0: 0.5ms, 1: 1.0ms, 2: 2.0ms, 3: 4.0ms                |

|          |                                      | REG1         | -                       | 0: 1400mA, 1: 1900mA                                  |

|          | Current Limit                        | REG2         | -                       | 0: 1400mA, 1: 1900mA                                  |

|          |                                      | REG3         | -                       | 0: 100mA, 1:200mA                                     |

|          | REG1DET                              | OV Detection | 11h[7:0]                | 0.60V ≤ Source ≤ 3.70V (in 12.5mV step)               |

|          | NEOIDEI                              | UV Detection | 10h[7:0]                | 0.60V ≤ Source ≤ 3.70V (in 12.5mV step)               |

| DETn     | REG2DET                              | OV Detection | 13h[7:0]                | $0.60V \le Source \le 3.70V$ (in 12.5mV step)         |

| DEIII    |                                      | UV Detection | 12h[7:0]                | 0.60V ≤ Source ≤ 3.70V (in 12.5mV step)               |

|          | REG3DET                              | OV Detection | 15h[7:0]                | 2.00V ≤ Source ≤ 4.00V (in 12.5mV step)               |

|          | NECODET                              | UV Detection | 14h[7:0]                | 2.00V ≤ Source ≤ 4.00V (in 12.5mV step)               |

Figure 32 Trimming Program

Refer to "Code List" for details.

<sup>(1)</sup> Program changeable register

No.EC-622-220627

### REGISTERS

#### **Registers Map**

| Address     | Block     | Name                     | Read<br>/Write | D7    | D6              | D5            | D4               | D3         | D2     | D1              | D0              | Initial<br>Value                      |

|-------------|-----------|--------------------------|----------------|-------|-----------------|---------------|------------------|------------|--------|-----------------|-----------------|---------------------------------------|

| 00h         | System    | LSIVER                   | R              |       | LSIVER[7:0]     |               |                  |            |        |                 | 8'h02           |                                       |

| 01h         |           | STATE                    | R              | -     | STATE[2:0]      |               |                  |            |        |                 | 8'h00           |                                       |

| 02h         |           | BISTCTRL                 | R/W            | -     | -               | -             | -                | -          | BIST_M | IENU[1:0]       | BISTEN          | 8'h00                                 |

| 03h         |           | BISTRESULT_L             | R              |       |                 |               | BIST_RE          | SULT[7:0]  |        |                 |                 | -                                     |

| 04h         |           | BISTRESULT_H             | R              |       |                 |               | BIST_RES         | SULT[15:8] |        |                 |                 | -                                     |

| 05h         |           | SYSCTRL                  | R,W            | ATREF | HS[1:0]         | ATREN         | UM[1:0]          | -          | -      | -               | SWREP           | Trimming                              |

| 06h         |           | AUTOOFF                  | R/W            | -     | -               | -             | -                | -          |        | DISAUTOOFF[3:0] |                 | 8'h00                                 |

| 07h         | -         | -                        | -              | -     | -               | -             | -                | -          | -      | -               | -               | -                                     |

| 08h         | Sequence  | REG1SEQ                  | R              | -     | -               | REG10         |                  | -          | -      |                 | FFT[1:0]        | Trimming                              |

| 09h         |           | REG2SEQ                  | R              | -     | -               | REG20         |                  | -          | -      |                 | 0FFT[1:0]       | Trimming                              |

| 0Ah         |           | REG3SEQ                  | R              | -     | -               | REG30         | NT[1:0]          | -          | -      | REG3C           | OFFT[1:0]       | Trimming                              |

| 0Bh         |           | RESETSEQ                 | R              | -     |                 | RESETONT[2:0] |                  | -          | -      | -               | -<br>.YTIM[1:0] | Trimming                              |

| 0Ch         |           | SLOTDTIM                 | R              | -     | -               | -             | -                | -          | -      |                 | YTIM[1:0]       | Trimming                              |

| 0Dh         | Power-    | REGCNT                   | R/W            | -     | -               | -             | -                | -          |        | REGDISOFF[2:0]  | T               | 8'h00                                 |

| 0Eh         | Source    | EXDETCNT                 | R/W            | -     | -               | -             | -                | -          | -      | -               | EXDETEN         | 8'h00                                 |

| 0Fh         | -         | -                        | -              | -     | -               | -             | -                | -          |        | -               | -               | -                                     |

| 10h         | DETCNT    | DETIDAC_UV               | R/W            |       |                 |               | DET1UV           |            |        |                 |                 | Trimming                              |

| 11h<br>12h  |           | DET1DAC_OV<br>DET2DAC_UV | R/W<br>R/W     |       |                 |               | DET10V<br>DET2UV | DAC[7:0]   |        |                 |                 | Trimming                              |

| 12n<br>13h  |           | DET2DAC_OV               | R/W            |       |                 |               |                  |            |        |                 |                 |                                       |

| 13n<br>14h  |           | DET3DAC_UV               | R/W            |       | DET20VDAC[7:0]  |               |                  |            |        |                 |                 | Trimming<br>Trimming                  |

| 14h<br>15h  |           | DET3DAC_OV               | R/W            |       |                 |               |                  |            |        |                 |                 |                                       |

|             |           | EXDETDAC_UV              | R/W            |       |                 |               |                  |            |        |                 |                 | Trimming                              |

| 16h<br>17h  |           | EXDETDAC OV              | R/W            |       | EXDETUVDAC(7:0) |               |                  |            |        |                 | 8'h00<br>8'h00  |                                       |

| 17h         | -         | -                        | -              |       | EXDETOVDAC[7:0] |               |                  |            |        |                 |                 |                                       |

| 19h         | -         |                          |                | -     |                 |               | -                |            | -      |                 | +               |                                       |

| 1911<br>1Ah | -         |                          |                | -     | -               |               | -                |            |        |                 | <u>+</u>        |                                       |

| 1Bh         | -         | -                        |                | -     | -               | -             |                  |            |        | +               | <u> </u>        |                                       |

| 1Ch         | -         | -                        | -              | -     | -               | -             | -                | -          | -      | -               | -               | -                                     |

| 1Dh         | -         | -                        | -              | -     | -               | -             | -                | -          | -      | -               | -               | -                                     |

| 1Eh         | -         | -                        | -              | -     | -               | -             | -                | -          | -      | -               | -               | -                                     |

| 1Fh         | -         | -                        | -              | -     | -               | -             | -                | -          | -      | -               | -               | -                                     |

| 20h         | Interrupt | INTREQ_L                 | R/W            |       |                 |               | INTRE            | Q[7:0]     |        |                 |                 | Undef                                 |

| 21h         |           | INTREQ_M                 | R/W            |       |                 |               |                  | Q[15:8]    |        |                 |                 | Undef                                 |

| 22h         |           | INTREQ_H                 | R/W            |       |                 |               | INTREC           | 2[16:24]   |        |                 |                 | Undef                                 |

| 23h         |           | VOLMON                   | R              |       |                 |               | VOLM             | ON[7:0]    |        |                 |                 | Undef                                 |

| 24h         |           | SYSMON                   | R              | -     | -               | -             | -                | -          | -      | CLKFREQ         | TEMPERATURE     | Undef                                 |

| 25h         |           | INTMSK_L                 | R/W            |       |                 |               | INTRE            |            |        |                 |                 | 8ħ00                                  |

| 26h         |           | INTMSK M                 | R/W            |       | INTREQ[15:8]    |               |                  |            |        |                 |                 | Trimming                              |

| 27h         |           | INTMSK_H                 | R/W            |       |                 |               |                  |            |        |                 |                 | 8ħ80                                  |

| 28h         |           | SHREQMSK L               | R/W            |       |                 |               |                  |            |        |                 |                 | 8"h00                                 |

| 29h         |           | SHREQMSK_H               | R/W            |       |                 |               | SHREQN           | ISK[15:8]  |        |                 |                 | 8'n07                                 |

| 2Ah         | -         | -                        |                | -     | -               | -             | -                | -          | -      |                 |                 |                                       |

| 2Bh         | -         | -                        |                | -     | -               | -             | -                |            | -      |                 |                 |                                       |

| 2Ch         | -         | -                        |                | -     | -               | -             | -                | -          | -      |                 |                 |                                       |

| 2Dh         | -         |                          |                | -     | -               | -             | -                |            | -      |                 |                 |                                       |

| 2Eh<br>2Fh  |           | -                        | <u> </u>       | -     | -               | -             |                  | Ξ          |        |                 |                 | · · · · · · · · · · · · · · · · · · · |